Difference between revisions of "PPC405"

Jump to navigation

Jump to search

m |

(not capitalised, bypass redirect) |

||

| Line 2: | Line 2: | ||

|title = Processor Information | |title = Processor Information | ||

|header1 = PowerPC 405 | |header1 = PowerPC 405 | ||

| − | |label2 = [[ | + | |label2 = [[Power ISA|Power ISA]] |

|data2 = v2.03 ([[Book_IIIE|Book III-E]]) | |data2 = v2.03 ([[Book_IIIE|Book III-E]]) | ||

|label3 = Process node | |label3 = Process node | ||

Revision as of 23:30, 19 January 2018

| PowerPC 405 | |

|---|---|

| Power ISA | v2.03 (Book III-E) |

| Process node | Variable |

| L1 cache | 16k data / 16k instruction |

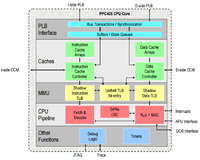

The PowerPC 405 is a long-lived embedded core, implementing the Power ISA v2.03 according to the Book III-E specification. It has seen use as an embedded controller in and around the POWER systems for quite some time, and is notable for being used to implement the POWER8 OCC functionality.