Difference between revisions of "OpenPOWER Firmware"

Jump to navigation

Jump to search

(add entry for OTPROM firmware) |

JeremyRand (talk | contribs) (→Components: CME HCODE upstream source) |

||

| (18 intermediate revisions by 5 users not shown) | |||

| Line 11: | Line 11: | ||

! Function | ! Function | ||

|- | |- | ||

| − | | [[OTPROM|OTPROM]] | + | | SBE - OTPROM |

| − | + | [https://git.raptorcs.com/git/talos-sbe/tree/src/boot/otprom_init.S Source] | |

| − | | eFuses | + | | [[Self-Boot Engine|SBE]] core (on CPU) |

| − | + | | [[OTPROM|OTPROM]] (on CPU die) | |

| + | | The portion of [[Self-Boot Engine|Self-Boot Engine]] (SBE) firmware permanently written via eFuses into the POWER9 silicon's OTPROM | ||

* very first instructions executed | * very first instructions executed | ||

| − | * loads SBE firmware from SEEPROM into SBE core | + | * loads remaining SBE firmware from SEEPROM into SBE core |

| + | |- | ||

| + | | SBE - SEEPROM | ||

| + | [https://git.raptorcs.com/git/talos-sbe/tree/ Source] | ||

| + | | [[Self-Boot Engine|SBE]] core (on CPU) | ||

| + | | SBE [[SEEPROM|SEEPROM]] (on CPU) | ||

| + | | The portion of [[Self-Boot Engine|Self-Boot Engine]] (SBE) firmware run from rewritable [[SEEPROM|SEEPROM]] | ||

| + | * initialises CPU core | ||

| + | * loads Hostboot Bootloader | ||

| + | * backup copy stored on PNOR SPI Flash, used to stage SBE firmware updates | ||

|- | |- | ||

| − | | [ | + | | Hostboot Bootloader (HBBL) |

| − | | SBE | + | [https://git.raptorcs.com/git/talos-hostboot/tree/src/bootloader Source] |

| − | + | | CPU core | |

| + | | SBE [[SEEPROM|SEEPROM]] (on CPU) | ||

| | | | ||

| − | * | + | * first code which runs on main CPU cores; loads and executes rest of Hostboot |

| − | * | + | * responsible for verifying integrity of Hostboot when secure boot is enabled, so this part of Hostboot is stored on the SBE SEEPROM, even though its source code lives inside the Hostboot repository |

|- | |- | ||

| [[Hostboot|Hostboot]] | | [[Hostboot|Hostboot]] | ||

| + | [https://git.raptorcs.com/git/talos-hostboot/tree/ Raptor Source] | ||

| + | [https://github.com/open-power/hostboot Upstream Source] | ||

| CPU core | | CPU core | ||

| − | | SPI Flash | + | | [[PNOR|PNOR]] (SPI Flash) |

| | | | ||

| − | * | + | * initialises DRAM (memory training, zeroing of ECC memory, etc.), processor bus, memory buffers |

| − | + | * finally, chainloads Skiboot | |

|- | |- | ||

| [[Skiboot|Skiboot]] | | [[Skiboot|Skiboot]] | ||

| + | [https://git.raptorcs.com/git/talos-skiboot/tree/ Raptor Source] | ||

| + | [https://github.com/open-power/skiboot Upstream Source] | ||

| CPU core | | CPU core | ||

| + | | [[PNOR|PNOR]] (SPI Flash) | ||

| | | | ||

| − | + | * initialises PCIe controllers, device trees, real time clock, NVlink, sensors | |

| − | * implements [[OpenPOWER Abstraction Layer|OpenPOWER Abstraction Layer]] (OPAL) for OS runtime services | + | * loads OCC firmware and starts OCC running |

| − | * | + | * implements [[OpenPOWER Abstraction Layer|OpenPOWER Abstraction Layer]] (OPAL) for OS runtime services; remains resident in RAM after OS boot |

| − | + | * finally, chainloads Skiroot | |

|- | |- | ||

| − | | [[Petitboot|Petitboot]] | + | | [[Skiroot]]/[[Petitboot|Petitboot]] |

| + | [https://git.raptorcs.com/git/talos-op-build/tree/openpower/configs/linux/skiroot_defconfig Skiroot Linux Config Source (Talos II)]<br> | ||

| + | [https://git.raptorcs.com/git/blackbird-op-build/tree/openpower/configs/linux/skiroot_defconfig Skiroot Linux Config Source (Blackbird)]<br> | ||

| + | [https://git.raptorcs.com/git/talos-petitboot/ Petitboot Source]<br> | ||

| + | [https://gitlab.raptorengineering.com/openpower-firmware/talos-op-build/-/blob/04-16-2019/openpower/configs/linux/skiroot_defconfig Skiroot Linux Config GitLab (Talos II)]<br> | ||

| + | [https://gitlab.raptorengineering.com/openpower-firmware/blackbird-op-build/-/blob/04-16-2019/openpower/configs/linux/skiroot_defconfig Skiroot Linux Config GitLab (Blackbird)] | ||

| CPU core | | CPU core | ||

| + | | [[PNOR|PNOR]] (SPI Flash) | ||

| | | | ||

| − | + | * [[Skiroot]] refers to the Linux kernel and initramfs which runs from RAM | |

| − | * boot menu | + | * Contains [[Petitboot]], a userspace application which provides a boot menu |

| − | * loads operating system | + | * [[Petitboot]] loads operating system via kexec |

| + | |- | ||

| + | | OCC firmware | ||

| + | [https://git.raptorcs.com/git/talos-occ/tree/ Raptor Source] | ||

| + | [https://github.com/open-power/occ Upstream Source] | ||

| + | | [[On-Chip Controller|OCC]] core (on CPU) | ||

| + | | [[PNOR|PNOR]] (SPI Flash) | ||

| + | | The [[On-Chip Controller|On-Chip Controller]] (OCC) manages: | ||

| + | * thermal regulation of CPU chip, turbo frequency selection, voltage ID selection, power measurement, etc. | ||

| + | |- | ||

| + | | CME [[HCODE]] | ||

| + | [https://git.raptorcs.com/git/talos-hcode/tree/ Raptor Source] | ||

| + | [https://github.com/open-power/hcode Upstream Source] | ||

| + | | [[CME]] cores (on CPU) | ||

| + | | [[PNOR|PNOR]] (SPI Flash) | ||

| + | | The [[Core Management Engine|Core Management Engines]] (CME) are auxillary cores used for power management purposes. They are ultimately responsible to the OCC. | ||

| + | * There is one CME for every pair of SMT4 cores. | ||

| + | |- | ||

| + | | SGPE and PGPE [[HCODE]] | ||

| + | [https://git.raptorcs.com/git/talos-hcode/tree/ Source] | ||

| + | | [[SGPE]] and [[PGPE]] cores (on CPU) | ||

| + | | [[PNOR|PNOR]] (SPI Flash) | ||

| + | | [[GPE|General Purpose Engine]] (GPE) cores which assist, and are managed by, the OCC. | ||

| + | * The [[SGPE|Stop GPEs]] (SGPEs) are part of the mechanism for resuming execution after a STOP instruction is executed (which is a Power ISA instruction which halts the processor). | ||

| + | * The [[PGPE|Pstate GPEs]] (PGPEs) perform pstate management. | ||

|- | |- | ||

| − | | [[ | + | | IOPPE [[HCODE]] |

| − | | | + | [https://git.raptorcs.com/git/talos-hcode/tree/ Source] |

| + | | [[IOPPE]] cores (on CPU) | ||

| + | | [[PNOR|PNOR]] (SPI Flash) | ||

| | | | ||

| + | * Involved in CAPI support. | ||

| + | |- style="background-color:#e0e0e0;" | ||

| + | | [[OpenBMC]] | ||

| + | [https://git.raptorcs.com/git/talos-openbmc/tree/ Source] | ||

| + | | BMC chip | ||

| + | | BMC SPI Flash | ||

| | | | ||

| − | * | + | <small>(This is not part of OpenPOWER firmware, but is mentioned to give a picture of the division of responsibilities. Not all POWER9 systems use a BMC; IBM systems use a [[FSP]].)</small> |

| + | * Turns system power rails on and off to energise and deenergise CPU modules, RAM, etc. | ||

| + | * Sends commands to CPU modules over [[FSI]] to commence booting. | ||

| + | * Provides access to PNOR SPI flash containing host firmware via LPC. | ||

| + | * Receives core temperature information from the [[OCC]]; decides and sets fan speeds. | ||

| + | * Powers off system if [[OCC]] indicates catastrophic temperature. | ||

|} | |} | ||

| + | |||

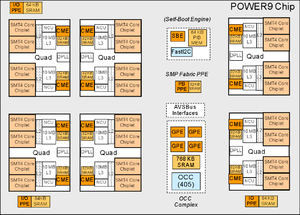

| + | [[File:P9_ppe_instances.png|thumb|Diagram of main and auxillary cores on [[POWER9]]]] | ||

== Process == | == Process == | ||

| − | # | + | # [[OpenBMC|OpenBMC]] uses [[FSI|FSI]] interface to start SBE |

| − | # [[ | + | # SBE executes [[OTPROM|OTPROM]], which loads SEEPROM firmware into SBE PIBMEM |

| + | # SBE executes SEEPROM firmware | ||

# [[Self-Boot Engine|SBE]] loads Hostboot | # [[Self-Boot Engine|SBE]] loads Hostboot | ||

# [[Hostboot|Hostboot]] loads Skiboot | # [[Hostboot|Hostboot]] loads Skiboot | ||

| − | # [[Skiboot|Skiboot]] loads OCC, | + | # [[Skiboot|Skiboot]] loads [[OCC]], [[Skiroot]] |

| − | # [[Petitboot|Petitboot]] loads the operating system | + | # [[Petitboot|Petitboot]] application within [[Skiroot]] loads the operating system |

| − | # | + | # OS talks to firmware through [[OpenPOWER Abstraction Layer|OPAL]] |

== References == | == References == | ||

| Line 72: | Line 134: | ||

* [[OpenBMC|OpenBMC]] | * [[OpenBMC|OpenBMC]] | ||

* [[OpenPOWER|OpenPOWER]] | * [[OpenPOWER|OpenPOWER]] | ||

| + | * [[Talos_II/Firmware]] | ||

| + | * [[Blackbird/Firmware]] | ||

== External Links == | == External Links == | ||

| − | * [https://github.com/open-power/docs OpenPOWER github | + | * [https://github.com/open-power/docs OpenPOWER firmware source code on GitHub] |

| − | * [https://github.com/open-power/docs OpenPOWER firmware documentation] | + | * '''For a better understanding of OpenPOWER firmware and boot processes, see:''' |

| − | * [https://blog.jms.id.au/2015/07/openpower-firmware-stack/ | + | ** [https://github.com/open-power/docs/blob/master/hostboot/HostBoot_PG.md Overview of Boot Process] |

| − | + | ** [https://github.com/open-power/docs/blob/master/hostboot/P9_Boot_Flow_OpenPOWER.pdf P9 Boot Flow] | |

| + | ** [https://github.com/open-power/docs More OpenPOWER firmware documentation] | ||

| + | ** [https://blog.jms.id.au/2015/07/openpower-firmware-stack/ OpenPOWER Firmware Stack] - Joel's Weblog | ||

| + | * Bug tracker for firmware issues specific to [[Raptor Computing Systems|Raptor CS]] products: https://bugs.raptorengineering.com/ | ||

[[Category:Firmware]] | [[Category:Firmware]] | ||

Latest revision as of 15:20, 3 March 2023

OpenPOWER Firmware is an open-source alternative to OpenFirmware and proprietary IBM firmware used on Power machines.[1] It is a general name for many separate pieces of software used to start recent Power Architecture chips made by IBM.[2]

OpenBMC is a separate project that creates firmware for the Baseboard Management Controller.

Components

| Firmware | Executed on | Loaded from | Function |

|---|---|---|---|

| SBE - OTPROM | SBE core (on CPU) | OTPROM (on CPU die) | The portion of Self-Boot Engine (SBE) firmware permanently written via eFuses into the POWER9 silicon's OTPROM

|

| SBE - SEEPROM | SBE core (on CPU) | SBE SEEPROM (on CPU) | The portion of Self-Boot Engine (SBE) firmware run from rewritable SEEPROM

|

| Hostboot Bootloader (HBBL) | CPU core | SBE SEEPROM (on CPU) |

|

| Hostboot | CPU core | PNOR (SPI Flash) |

|

| Skiboot | CPU core | PNOR (SPI Flash) |

|

| Skiroot/Petitboot

Skiroot Linux Config Source (Talos II) |

CPU core | PNOR (SPI Flash) | |

| OCC firmware | OCC core (on CPU) | PNOR (SPI Flash) | The On-Chip Controller (OCC) manages:

|

| CME HCODE | CME cores (on CPU) | PNOR (SPI Flash) | The Core Management Engines (CME) are auxillary cores used for power management purposes. They are ultimately responsible to the OCC.

|

| SGPE and PGPE HCODE | SGPE and PGPE cores (on CPU) | PNOR (SPI Flash) | General Purpose Engine (GPE) cores which assist, and are managed by, the OCC.

|

| IOPPE HCODE | IOPPE cores (on CPU) | PNOR (SPI Flash) |

|

| OpenBMC | BMC chip | BMC SPI Flash |

(This is not part of OpenPOWER firmware, but is mentioned to give a picture of the division of responsibilities. Not all POWER9 systems use a BMC; IBM systems use a FSP.)

|

Diagram of main and auxillary cores on POWER9

Process

- OpenBMC uses FSI interface to start SBE

- SBE executes OTPROM, which loads SEEPROM firmware into SBE PIBMEM

- SBE executes SEEPROM firmware

- SBE loads Hostboot

- Hostboot loads Skiboot

- Skiboot loads OCC, Skiroot

- Petitboot application within Skiroot loads the operating system

- OS talks to firmware through OPAL

References

- ↑ Kerr, Jeremy. OpenPOWER: building an open-source software stack from bare metal. LCA 2015 - video on YouTube

- ↑ Smith, Stewart. Adventures in OpenPOWER Firmware. LCA 2016 - video on YouTube

See also

External Links

- OpenPOWER firmware source code on GitHub

- For a better understanding of OpenPOWER firmware and boot processes, see:

- Bug tracker for firmware issues specific to Raptor CS products: https://bugs.raptorengineering.com/