Difference between revisions of "OpenPOWER Firmware"

Jump to navigation

Jump to search

m (→External Links: add link: https://bugs.raptorengineering.com/) |

(→Components: keeping links to hardware components out of firmware column, adding SEEPROM location, linking to more glossary pages) |

||

| Line 13: | Line 13: | ||

| [[OTPROM|OTPROM]] | | [[OTPROM|OTPROM]] | ||

| SBE core (on CPU chip) | | SBE core (on CPU chip) | ||

| − | | eFuses | + | | eFuses (on CPU module) |

[https://git.raptorcs.com/git/talos-sbe/tree/src/boot/otprom_init.S Source] | [https://git.raptorcs.com/git/talos-sbe/tree/src/boot/otprom_init.S Source] | ||

| | | | ||

| Line 21: | Line 21: | ||

| [[Self-Boot Engine|Self-Boot Engine]] (SBE) firmware | | [[Self-Boot Engine|Self-Boot Engine]] (SBE) firmware | ||

| SBE core (on CPU chip) | | SBE core (on CPU chip) | ||

| − | | SBE SEEPROM | + | | SBE [[SEEPROM|SEEPROM]] (on CPU module) |

[https://git.raptorcs.com/git/talos-sbe/tree/ Source] | [https://git.raptorcs.com/git/talos-sbe/tree/ Source] | ||

| | | | ||

| Line 30: | Line 30: | ||

| Hostboot Bootloader (HBBL) | | Hostboot Bootloader (HBBL) | ||

| CPU core | | CPU core | ||

| − | | SBE SEEPROM | + | | SBE SEEPROM (on CPU chip) |

[https://git.raptorcs.com/git/talos-hostboot/tree/src/bootloader Source] | [https://git.raptorcs.com/git/talos-hostboot/tree/src/bootloader Source] | ||

| | | | ||

| Line 38: | Line 38: | ||

| [[Hostboot|Hostboot]] | | [[Hostboot|Hostboot]] | ||

| CPU core | | CPU core | ||

| − | | PNOR SPI Flash | + | | [[PNOR|PNOR]] (SPI Flash) |

[https://git.raptorcs.com/git/talos-hostboot/tree/ Source] | [https://git.raptorcs.com/git/talos-hostboot/tree/ Source] | ||

| | | | ||

| Line 46: | Line 46: | ||

| [[Skiboot|Skiboot]] | | [[Skiboot|Skiboot]] | ||

| CPU core | | CPU core | ||

| − | | PNOR SPI Flash | + | | [[PNOR|PNOR]] (SPI Flash) |

[https://git.raptorcs.com/git/talos-skiboot/tree/ Source] | [https://git.raptorcs.com/git/talos-skiboot/tree/ Source] | ||

| | | | ||

| Line 56: | Line 56: | ||

| [[Skiroot]]/[[Petitboot|Petitboot]] | | [[Skiroot]]/[[Petitboot|Petitboot]] | ||

| CPU core | | CPU core | ||

| − | | PNOR SPI Flash | + | | [[PNOR|PNOR]] (SPI Flash) |

[https://git.raptorcs.com/git/talos-petitboot/ Source] | [https://git.raptorcs.com/git/talos-petitboot/ Source] | ||

| | | | ||

| Line 63: | Line 63: | ||

* [[Petitboot]] loads operating system via kexec | * [[Petitboot]] loads operating system via kexec | ||

|- | |- | ||

| − | | [[On-Chip Controller| | + | | OCC firmware |

| − | + | | [[On-Chip Controller|OCC]] core (on CPU chip) | |

| − | | PNOR SPI Flash | + | | [[PNOR|PNOR]] (SPI Flash) |

[https://git.raptorcs.com/git/talos-occ/tree/ Source] | [https://git.raptorcs.com/git/talos-occ/tree/ Source] | ||

| − | | | + | | The [[On-Chip Controller|On-Chip Controller]] (OCC) manages: |

* thermal regulation of CPU chip, turbo frequency selection, voltage ID selection, power measurement, etc. | * thermal regulation of CPU chip, turbo frequency selection, voltage ID selection, power measurement, etc. | ||

|- | |- | ||

| − | | | + | | CME [[HCODE]] |

| [[CME]] cores (on CPU chip) | | [[CME]] cores (on CPU chip) | ||

| − | | PNOR SPI Flash | + | | [[PNOR|PNOR]] (SPI Flash) |

[https://git.raptorcs.com/git/talos-hcode/tree/ Source] | [https://git.raptorcs.com/git/talos-hcode/tree/ Source] | ||

| − | | | + | | The [[Core Management Engine|Core Management Engines]] (CME) are auxillary cores used for power management purposes. They are ultimately responsible to the OCC. |

| − | + | * There is one CME for every pair of SMT4 cores. | |

|- | |- | ||

| − | | | + | | SGPE and PGPE [[HCODE]] |

| − | + | | [[SGPE]] and [[PGPE]] cores (on CPU chip) | |

| − | | PNOR SPI Flash | + | | [[PNOR|PNOR]] (SPI Flash) |

[https://git.raptorcs.com/git/talos-hcode/tree/ Source] | [https://git.raptorcs.com/git/talos-hcode/tree/ Source] | ||

| − | | | + | | [[GPE|General Purpose Engine]] (GPE) cores which assist, and are managed by, the OCC. |

| − | |||

* The [[SGPE|Stop GPEs]] (SGPEs) are part of the mechanism for resuming execution after a STOP instruction is executed (which is a Power ISA instruction which halts the processor). | * The [[SGPE|Stop GPEs]] (SGPEs) are part of the mechanism for resuming execution after a STOP instruction is executed (which is a Power ISA instruction which halts the processor). | ||

* The [[PGPE|Pstate GPEs]] (PGPEs) perform pstate management. | * The [[PGPE|Pstate GPEs]] (PGPEs) perform pstate management. | ||

|- | |- | ||

| − | | | + | | IOPPE [[HCODE]] |

| [[IOPPE]] cores (on CPU chip) | | [[IOPPE]] cores (on CPU chip) | ||

| − | | PNOR SPI Flash | + | | [[PNOR|PNOR]] (SPI Flash) |

[https://git.raptorcs.com/git/talos-hcode/tree/ Source] | [https://git.raptorcs.com/git/talos-hcode/tree/ Source] | ||

| | | | ||

Revision as of 10:43, 30 June 2021

OpenPOWER Firmware is an open-source alternative to OpenFirmware and proprietary IBM firmware used on Power machines.[1] It is a general name for many separate pieces of software used to start recent Power Architecture chips made by IBM.[2]

OpenBMC is a separate project that creates firmware for the Baseboard Management Controller.

Components

| Firmware | Executed on | Loaded from | Function |

|---|---|---|---|

| OTPROM | SBE core (on CPU chip) | eFuses (on CPU module) |

|

| Self-Boot Engine (SBE) firmware | SBE core (on CPU chip) | SBE SEEPROM (on CPU module) |

|

| Hostboot Bootloader (HBBL) | CPU core | SBE SEEPROM (on CPU chip) |

|

| Hostboot | CPU core | PNOR (SPI Flash) |

|

| Skiboot | CPU core | PNOR (SPI Flash) |

|

| Skiroot/Petitboot | CPU core | PNOR (SPI Flash) | |

| OCC firmware | OCC core (on CPU chip) | PNOR (SPI Flash) | The On-Chip Controller (OCC) manages:

|

| CME HCODE | CME cores (on CPU chip) | PNOR (SPI Flash) | The Core Management Engines (CME) are auxillary cores used for power management purposes. They are ultimately responsible to the OCC.

|

| SGPE and PGPE HCODE | SGPE and PGPE cores (on CPU chip) | PNOR (SPI Flash) | General Purpose Engine (GPE) cores which assist, and are managed by, the OCC.

|

| IOPPE HCODE | IOPPE cores (on CPU chip) | PNOR (SPI Flash) |

|

| OpenBMC | BMC chip | BMC SPI Flash |

(This is not part of OpenPOWER firmware, but is mentioned to give a picture of the division of responsibilities. Not all POWER9 systems use a BMC; IBM systems use a FSP.)

|

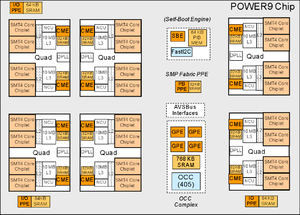

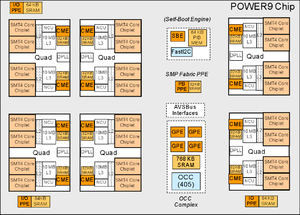

Diagram of main and auxillary cores on POWER9

Process

- SBE executes OTPROM, which loads SEEPROM firmware into SBE PIBMEM

- SBE executes SEEPROM firmware

- OpenBMC uses FSI interface to start SBE

- SBE loads Hostboot

- Hostboot loads Skiboot

- Skiboot loads OCC, Skiroot

- Petitboot application within Skiroot loads the operating system

- OS talks to firmware through OPAL

References

- ↑ Kerr, Jeremy. OpenPOWER: building an open-source software stack from bare metal. LCA 2015 - video on YouTube

- ↑ Smith, Stewart. Adventures in OpenPOWER Firmware. LCA 2016 - video on YouTube

See also

External Links

- OpenPOWER firmware source code on GitHub

- For a better understanding of OpenPOWER firmware and boot processes, see:

- Bug tracker for firmware issues specific to Raptor CS products: https://bugs.raptorengineering.com/