Power Systems Host Bridge 4 (PHB4) Specification

OpenPOWER

Version 1.0 27 July 2018

#### © Copyright International Business Machines Corporation 2018

Printed in the United States of America July 2018

IBM, the IBM logo, and ibm.com are trademarks or registered trademarks of International Business Machines Corp., registered in many jurisdictions worldwide. Other product and service names might be trademarks of IBM or other companies. A current list of IBM trademarks is available on the Web at "Copyright and trademark information" at <a href="http://www.ibm.com/legal/copytrade.shtml">www.ibm.com/legal/copytrade.shtml</a>.

Intel, Intel Iogo, Intel Inside, Intel Inside Iogo, Intel Centrino, Intel Centrino Iogo, Celeron, Intel Xeon, Intel SpeedStep, Itanium, and Pentium are trademarks or registered trademarks of Intel Corporation or its subsidiaries in the United States and other countries.

Linux is a registered trademark of Linus Torvalds in the United States, other countries, or both.

The OpenPOWER word mark and the OpenPOWER Logo mark, and related marks, are trademarks and service marks licensed by OpenPOWER.

Other company, product, and service names may be trademarks or service marks of others.

All information contained in this document is subject to change without notice. The products described in this document are NOT intended for use in applications such as implantation, life support, or other hazardous uses where malfunction could result in death, bodily injury, or catastrophic property damage. The information contained in this document does not affect or change IBM product specifications or warranties. Nothing in this document shall operate as an express or implied indemnity under the intellectual property rights of IBM or third parties. All information contained in this document was obtained in specific environments, and is presented as an illustration. The results obtained in other operating environments may vary.

This document is intended for the development of technology products compatible with Power Architecture®. You may use this document, for any purpose (commercial or personal) and make modifications and distribute; however, modifications to this document may violate Power Architecture and should be carefully considered. Any distribution of this document or its derivative works shall include this Notice page including but not limited to the IBM warranty disclaimer and IBM liability limitation. No other licenses (including patent licenses), expressed or implied, by estoppel or otherwise, to any intellectual property rights are granted by this document.

THE INFORMATION CONTAINED IN THIS DOCUMENT IS PROVIDED ON AN "AS IS" BASIS. IBM makes no representations or warranties, either express or implied, including but not limited to, warranties of merchantability, fitness for a particular purpose, or non-infringement, or that any practice or implementation of the IBM documentation will not infringe any third party patents, copyrights, trade secrets, or other rights. In no event will IBM be liable for damages arising directly or indirectly from any use of the information contained in this document.

IBM Systems 294 Route 100, Building SOM4 Somers, NY 10589-3216

The IBM home page can be found at ibm.com®.

Version 1.0 27 July 2018

# Contents

| List of Figures                                                         | 11   |

|-------------------------------------------------------------------------|------|

| List of Tables                                                          | 13   |

| Revision Log                                                            | 15   |

| About this Document                                                     | 17   |

| Who Should Read this Document                                           | . 17 |

| Related Documents                                                       | . 17 |

| Terminology Used in this Document                                       | . 17 |

| Conventions Used in This Document                                       |      |

| Typographical Conventions                                               |      |

| Representation of Numbers                                               | . 17 |

| 1. Introduction                                                         | 19   |

| 2. Requirements                                                         | 20   |

| 2.1 ETU Specific Requirements                                           | . 20 |

| 2.1.1 Features                                                          | . 20 |

| 2.1.2 Interfaces and Protocols                                          |      |

| 2.1.3 Functions                                                         |      |

| 2.1.3.1 General functions                                               |      |

| 2.1.3.2 Specific IBM methodology support functions                      |      |

| 2.2 PCIe Specific Requirements                                          |      |

| 2.2.1 Features                                                          |      |

| 2.2.2 Interfaces and Protocols                                          |      |

| 2.2.3 Functions                                                         |      |

| 2.2.3.1 General functions:                                              |      |

| 2.2.3.2 Power Management Features                                       |      |

| 2.2.3.3 Specific IBM methodology support<br>2.2.3.4 Other PCIe Features |      |

| 2.3 PHB4 Common Requirements                                            |      |

| 2.3.1 Features                                                          |      |

|                                                                         |      |

| 3. Functional Description                                               | 29   |

| 3.1 PHB4 Command Details                                                | . 29 |

| 3.1.1 Other Command details                                             | . 30 |

| 3.2 Ordering Rules                                                      | . 34 |

| 3.3 Interrupt Types                                                     | . 35 |

| 3.3.1 LSI Interrupts                                                    |      |

| 3.3.2 MSI Interrupts                                                    |      |

| 3.3.3 Error Interrupts                                                  | . 36 |

| 3.4 Interrupt Logic                                                     | . 36 |

| 3.5 Transaction Logic                                                   |      |

| 3.5.1 MMIO Transactions                                                 | . 37 |

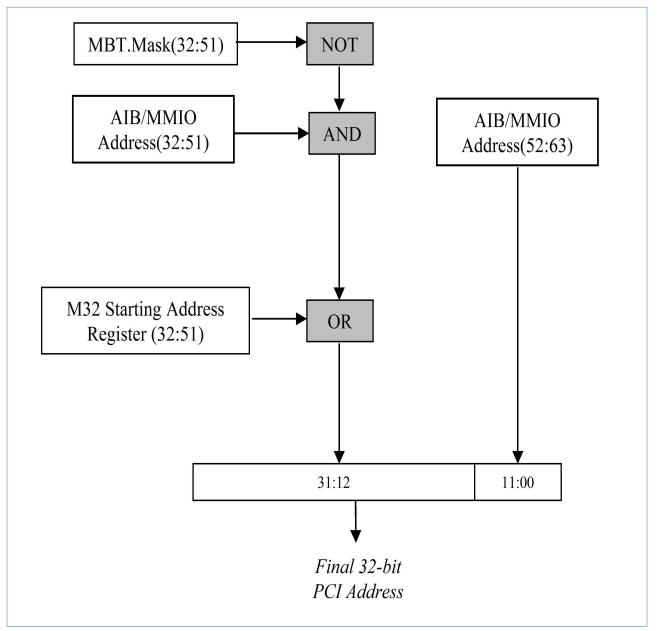

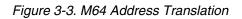

| 3.5.1.1 MMIO Address Translation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                          |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 38                                                                                                                                                       |

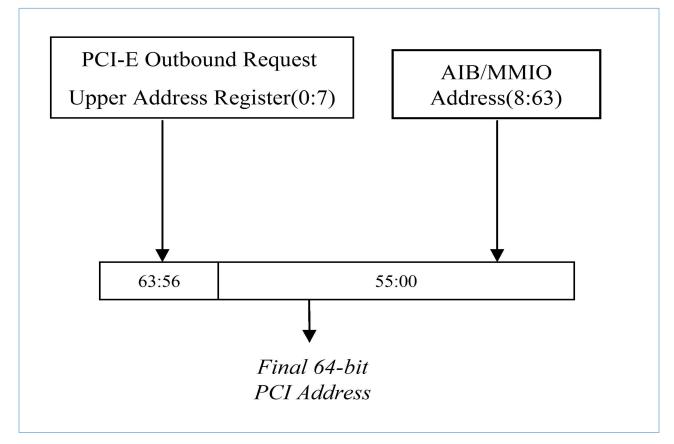

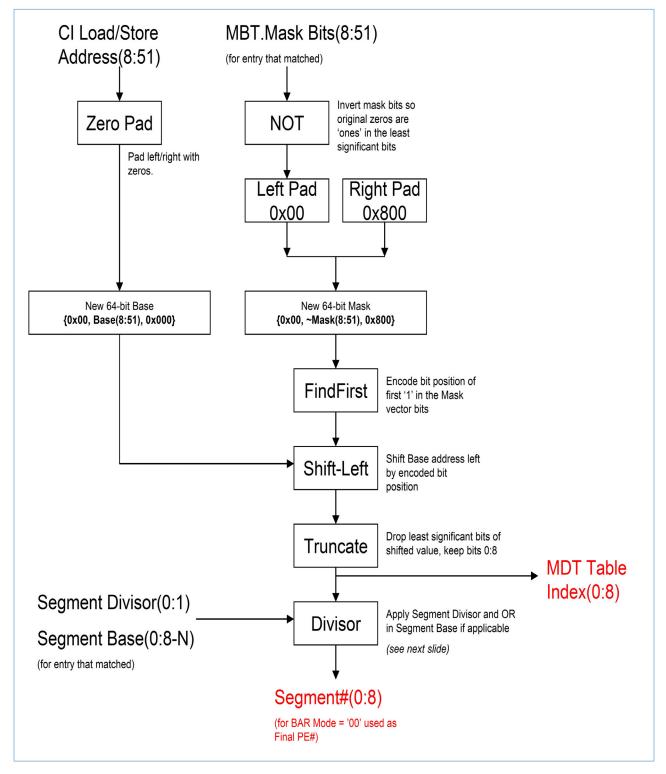

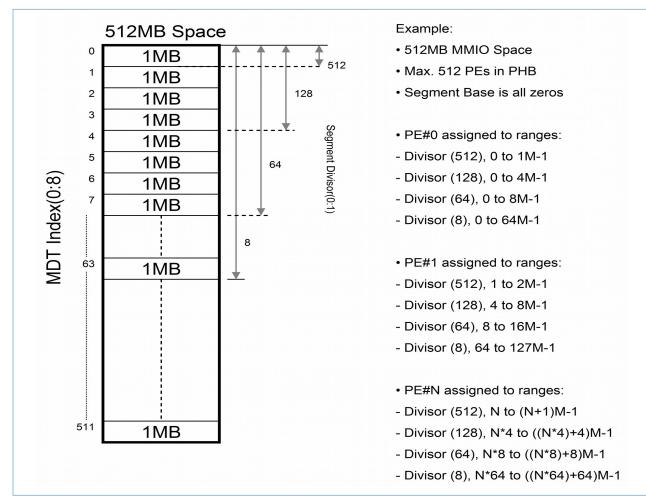

| 3.5.1.2 MMIO to PE Number Mapping                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 40                                                                                                                                                       |

| 3.6 Nontranslate/Untranslated Addresses                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 44                                                                                                                                                       |

| 3.7 Error Logic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 45                                                                                                                                                       |

| 3.7.1 Error Classification                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                          |

| 3.7.1.1 INF Class                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 45                                                                                                                                                       |

| 3.7.1.2 ER Class                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 46                                                                                                                                                       |

| 3.7.1.3 Fatal/PHB4 Class                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 46                                                                                                                                                       |

| 3.7.2 Error Detection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                          |

| 3.7.2.1 LEM and Error Trap Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                          |

| 3.7.2.2 PCIe Errors (detected by PCIe cores)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 47                                                                                                                                                       |

| 3.7.2.3 Timeouts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 47                                                                                                                                                       |

| 3.7.3 Error Reporting                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                          |

| 3.7.3.1 Error Interrupts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                          |

| 3.7.4 Error Handling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                          |

| 3.7.4.1 INF Class Error Handling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                          |

| 3.7.4.2 ER Class Error Handling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                          |

| 3.7.4.3 Fatal/PHB4 Class Error Handling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                          |

| 3.7.5 Error Recovery                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                          |

| 3.7.5.1 Recovery Sequences                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                          |

| 3.7.6 Error Injection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 54                                                                                                                                                       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                          |

| 4. Software Interfaces                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 55                                                                                                                                                       |

| 4.1 Register Definitions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 55                                                                                                                                                       |

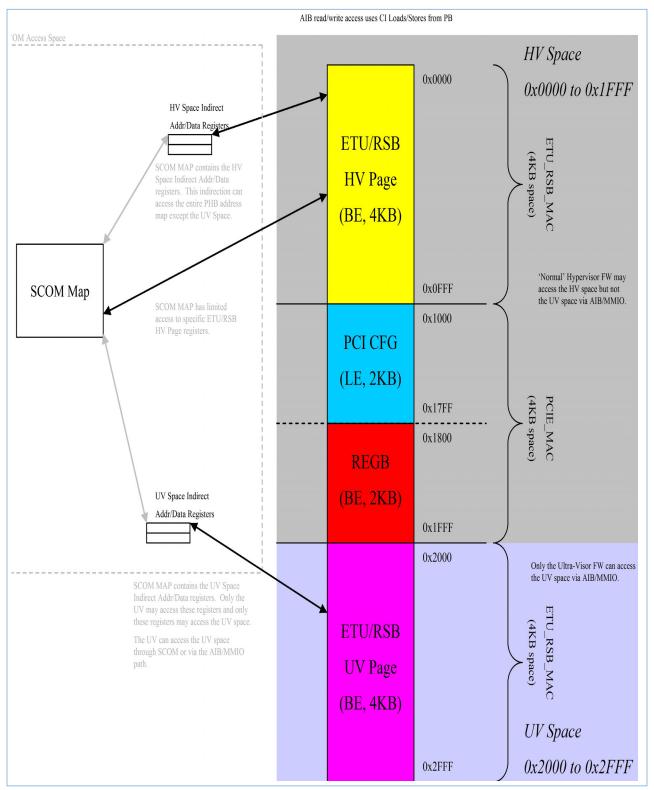

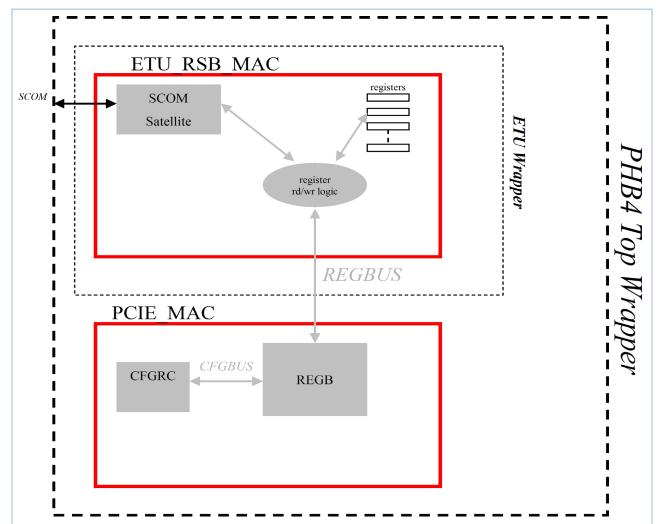

| 4.2 PHB4 Unified Address Space                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 56                                                                                                                                                       |

| 4.3 SCOM Registers (ETU)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                          |

| 4.3.1 SCOM Register Áddress Map                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                          |

| 4.3.2 SCOM Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 60                                                                                                                                                       |

| 4.3.2 SCOM Registers<br>4.3.2.1 SCOM - HV Indirect Address Register<br>4.3.2.2 SCOM HV Indirect Data Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 60<br>60                                                                                                                                                 |

| 4.3.2.1 SCOM - HV Indirect Address Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 60<br>60<br>61                                                                                                                                           |

| 4.3.2.1 SCOM - HV Indirect Address Register<br>4.3.2.2 SCOM HV Indirect Data Register<br>4.3.2.3 SCOM Direct Mapped Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 60<br>60<br>61<br>61                                                                                                                                     |

| <ul> <li>4.3.2.1 SCOM - HV Indirect Address Register</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 60<br>60<br>61<br>61<br>62                                                                                                                               |

| <ul> <li>4.3.2.1 SCOM - HV Indirect Address Register</li> <li>4.3.2.2 SCOM HV Indirect Data Register</li> <li>4.3.2.3 SCOM Direct Mapped Registers</li> <li>4.4 ETU/RSB HV Registers</li> <li>4.4.1 ETU/RSB HV Register Address Map</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 60<br>60<br>61<br>61<br>62<br>62                                                                                                                         |

| <ul> <li>4.3.2.1 SCOM - HV Indirect Address Register</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 60<br>61<br>61<br>61<br>62<br>62<br>67                                                                                                                   |

| <ul> <li>4.3.2.1 SCOM - HV Indirect Address Register</li> <li>4.3.2.2 SCOM HV Indirect Data Register</li> <li>4.3.2.3 SCOM Direct Mapped Registers</li> <li>4.4 ETU/RSB HV Registers</li> <li>4.4.1 ETU/RSB HV Register Address Map</li> <li>4.4.2 Fundamental Register Set A</li> <li>4.4.2.1 LSI SourceID Register</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 60<br>61<br>61<br>62<br>62<br>67<br>67                                                                                                                   |

| <ul> <li>4.3.2.1 SCOM - HV Indirect Address Register</li> <li>4.3.2.2 SCOM HV Indirect Data Register</li> <li>4.3.2.3 SCOM Direct Mapped Registers</li> <li>4.4 ETU/RSB HV Registers</li> <li>4.4.1 ETU/RSB HV Register Address Map</li> <li>4.4.2 Fundamental Register Set A</li> <li>4.4.2.1 LSI SourceID Register</li> <li>4.4.2.2 DMA Channel Status Register</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 60<br>61<br>61<br>61<br>62<br>62<br>67<br>67<br>68                                                                                                       |

| <ul> <li>4.3.2.1 SCOM - HV Indirect Address Register</li> <li>4.3.2.2 SCOM HV Indirect Data Register</li> <li>4.3.2.3 SCOM Direct Mapped Registers</li> <li>4.4 ETU/RSB HV Registers</li> <li>4.4.1 ETU/RSB HV Register Address Map</li> <li>4.4.2 Fundamental Register Set A</li> <li>4.4.2.1 LSI SourceID Register</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 60<br>61<br>61<br>62<br>62<br>62<br>67<br>67<br>68<br>68                                                                                                 |

| <ul> <li>4.3.2.1 SCOM - HV Indirect Address Register</li> <li>4.3.2.2 SCOM HV Indirect Data Register</li> <li>4.3.2.3 SCOM Direct Mapped Registers</li> <li>4.4 ETU/RSB HV Registers</li> <li>4.4.1 ETU/RSB HV Register Address Map</li> <li>4.4.2 Fundamental Register Set A</li> <li>4.4.2.1 LSI SourceID Register</li> <li>4.4.2.2 DMA Channel Status Register</li> <li>4.4.2.3 Processor Load/Store Status Register</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                  | 60<br>60<br>61<br>61<br>62<br>62<br>67<br>67<br>67<br>68<br>68<br>68<br>68<br>69                                                                         |

| <ul> <li>4.3.2.1 SCOM - HV Indirect Address Register</li> <li>4.3.2.2 SCOM HV Indirect Data Register</li> <li>4.3.2.3 SCOM Direct Mapped Registers</li> <li>4.4 ETU/RSB HV Registers</li> <li>4.4.1 ETU/RSB HV Register Address Map</li> <li>4.4.2 Fundamental Register Set A</li> <li>4.4.2.1 LSI SourceID Register</li> <li>4.4.2.2 DMA Channel Status Register</li> <li>4.4.2.3 Processor Load/Store Status Register</li> <li>4.4.2.4 CONFIG_DATA Register</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                            | 60<br>60<br>61<br>61<br>62<br>62<br>67<br>67<br>67<br>67<br>68<br>68<br>68<br>68<br>70                                                                   |

| <ul> <li>4.3.2.1 SCOM - HV Indirect Address Register</li> <li>4.3.2.2 SCOM HV Indirect Data Register</li> <li>4.3.2.3 SCOM Direct Mapped Registers</li> <li>4.4 ETU/RSB HV Registers</li> <li>4.4.1 ETU/RSB HV Register Address Map</li> <li>4.4.2 Fundamental Register Set A</li> <li>4.4.2.1 LSI SourceID Register</li> <li>4.4.2.2 DMA Channel Status Register</li> <li>4.4.2.3 Processor Load/Store Status Register</li> <li>4.4.2.4 CONFIG_DATA Register</li> <li>4.4.2.5 Lock0 Register</li> </ul>                                                                                                                                                                                                                                                                                                                                                            | 60<br>60<br>61<br>61<br>62<br>62<br>62<br>67<br>67<br>67<br>67<br>68<br>68<br>68<br>68<br>69<br>70<br>71                                                 |

| <ul> <li>4.3.2.1 SCOM - HV Indirect Address Register</li> <li>4.3.2.2 SCOM HV Indirect Data Register</li> <li>4.3.2.3 SCOM Direct Mapped Registers</li> <li>4.4 ETU/RSB HV Registers</li> <li>4.4.1 ETU/RSB HV Register Address Map</li> <li>4.4.2 Fundamental Register Set A</li> <li>4.4.2.1 LSI SourceID Register</li> <li>4.4.2.2 DMA Channel Status Register</li> <li>4.4.2.3 Processor Load/Store Status Register</li> <li>4.4.2.4 CONFIG_DATA Register</li> <li>4.4.2.5 Lock0 Register</li> <li>4.4.2.6 CONFIG_ADDRESS Register</li> </ul>                                                                                                                                                                                                                                                                                                                   | 60<br>60<br>61<br>61<br>62<br>62<br>62<br>67<br>67<br>67<br>67<br>68<br>68<br>68<br>68<br>70<br>71<br>72                                                 |

| <ul> <li>4.3.2.1 SCOM - HV Indirect Address Register</li> <li>4.3.2.2 SCOM HV Indirect Data Register</li> <li>4.3.2.3 SCOM Direct Mapped Registers</li> <li>4.4 ETU/RSB HV Registers</li> <li>4.4.1 ETU/RSB HV Register Address Map</li> <li>4.4.2 Fundamental Register Set A</li> <li>4.4.2.1 LSI SourceID Register</li> <li>4.4.2.2 DMA Channel Status Register</li> <li>4.4.2.3 Processor Load/Store Status Register</li> <li>4.4.2.4 CONFIG_DATA Register</li> <li>4.4.2.5 Lock0 Register</li> <li>4.4.2.7 Lock1 Register</li> </ul>                                                                                                                                                                                                                                                                                                                            | 60<br>60<br>61<br>61<br>62<br>62<br>62<br>67<br>67<br>67<br>68<br>68<br>68<br>68<br>70<br>71<br>72<br>73                                                 |

| <ul> <li>4.3.2.1 SCOM - HV Indirect Address Register</li> <li>4.3.2.2 SCOM HV Indirect Data Register</li> <li>4.3.2.3 SCOM Direct Mapped Registers</li> <li>4.4 ETU/RSB HV Registers</li> <li>4.4.1 ETU/RSB HV Register Address Map</li> <li>4.4.2 Fundamental Register Set A</li> <li>4.4.2.1 LSI SourceID Register</li> <li>4.4.2.2 DMA Channel Status Register</li> <li>4.4.2.3 Processor Load/Store Status Register</li> <li>4.4.2.4 CONFIG_DATA Register</li> <li>4.4.2.5 Lock0 Register</li> <li>4.4.2.6 CONFIG_ADDRESS Register</li> <li>4.4.2.7 Lock1 Register</li> <li>4.4.2.8 PHB4 Configuration Register</li> <li>4.4.2.9 RTT Base Address Register</li> <li>4.4.2.10 PELT-V Base Address Register</li> </ul>                                                                                                                                            | 60<br>61<br>61<br>62<br>62<br>62<br>67<br>67<br>67<br>67<br>68<br>68<br>68<br>69<br>70<br>71<br>72<br>73<br>74<br>74<br>74                               |

| <ul> <li>4.3.2.1 SCOM - HV Indirect Address Register</li> <li>4.3.2.2 SCOM HV Indirect Data Register</li> <li>4.3.2.3 SCOM Direct Mapped Registers</li> <li>4.4 ETU/RSB HV Registers</li> <li>4.4.1 ETU/RSB HV Register Address Map</li> <li>4.4.2 Fundamental Register Set A</li> <li>4.4.2.1 LSI SourceID Register</li> <li>4.4.2.2 DMA Channel Status Register</li> <li>4.4.2.3 Processor Load/Store Status Register</li> <li>4.4.2.4 CONFIG_DATA Register</li> <li>4.4.2.5 Lock0 Register</li> <li>4.4.2.7 Lock1 Register</li> <li>4.4.2.8 PHB4 Configuration Register</li> <li>4.4.2.9 RTT Base Address Register</li> <li>4.4.2.10 PELT-V Base Address Register</li> <li>4.4.2.11 M32 Starting Address Register</li> </ul>                                                                                                                                     | 60<br>60<br>61<br>61<br>62<br>62<br>62<br>67<br>67<br>67<br>67<br>68<br>68<br>69<br>70<br>71<br>72<br>73<br>74<br>74<br>                                 |

| <ul> <li>4.3.2.1 SCOM - HV Indirect Address Register</li> <li>4.3.2.2 SCOM HV Indirect Data Register</li> <li>4.3.2.3 SCOM Direct Mapped Registers</li> <li>4.4 ETU/RSB HV Registers</li> <li>4.4.1 ETU/RSB HV Register Address Map</li> <li>4.4.2 Fundamental Register Set A</li> <li>4.4.2.1 LSI SourceID Register</li> <li>4.4.2.2 DMA Channel Status Register</li> <li>4.4.2.3 Processor Load/Store Status Register</li> <li>4.4.2.4 CONFIG_DATA Register</li> <li>4.4.2.5 Lock0 Register</li> <li>4.4.2.6 CONFIG_ADDRESS Register</li> <li>4.4.2.7 Lock1 Register</li> <li>4.4.2.8 PHB4 Configuration Register</li> <li>4.4.2.9 RTT Base Address Register</li> <li>4.4.2.10 PELT-V Base Address Register</li> </ul>                                                                                                                                            | 60<br>60<br>61<br>61<br>62<br>62<br>62<br>67<br>67<br>67<br>67<br>68<br>68<br>69<br>70<br>71<br>72<br>73<br>74<br>74<br>                                 |

| <ul> <li>4.3.2.1 SCOM - HV Indirect Address Register</li> <li>4.3.2.2 SCOM HV Indirect Data Register</li> <li>4.3.2.3 SCOM Direct Mapped Registers</li> <li>4.4 ETU/RSB HV Registers</li> <li>4.4 ETU/RSB HV Register Address Map</li> <li>4.1 ETU/RSB HV Register Address Map</li> <li>4.2 Fundamental Register Set A</li> <li>4.2.1 LSI SourceID Register</li> <li>4.4.2.2 DMA Channel Status Register</li> <li>4.4.2.3 Processor Load/Store Status Register</li> <li>4.4.2.4 CONFIG_DATA Register</li> <li>4.4.2.5 Lock0 Register</li> <li>4.4.2.6 CONFIG_ADDRESS Register</li> <li>4.4.2.7 Lock1 Register</li> <li>4.4.2.8 PHB4 Configuration Register</li> <li>4.4.2.10 PELT-V Base Address Register</li> <li>4.4.2.11 M32 Starting Address Register</li> <li>4.4.2.12 PEST Base Address Register</li> <li>4.4.2.13 CRW Base Address Register</li> </ul>       | 60<br>60<br>61<br>61<br>62<br>62<br>62<br>67<br>67<br>67<br>67<br>68<br>68<br>68<br>68<br>69<br>70<br>71<br>72<br>73<br>74<br>74<br>75<br>75<br>76       |

| <ul> <li>4.3.2.1 SCOM - HV Indirect Address Register</li> <li>4.3.2.2 SCOM HV Indirect Data Register</li> <li>4.3.2.3 SCOM Direct Mapped Registers</li> <li>4.4 ETU/RSB HV Registers</li> <li>4.4.1 ETU/RSB HV Register Address Map</li> <li>4.4.2 Fundamental Register Set A</li> <li>4.4.2.1 LSI SourceID Register</li> <li>4.4.2.2 DMA Channel Status Register</li> <li>4.4.2.3 Processor Load/Store Status Register</li> <li>4.4.2.4 CONFIG_DATA Register</li> <li>4.4.2.5 Lock0 Register</li> <li>4.4.2.6 CONFIG_ADDRESS Register</li> <li>4.4.2.8 PHB4 Configuration Register</li> <li>4.4.2.9 RTT Base Address Register</li> <li>4.4.2.10 PELT-V Base Address Register</li> <li>4.4.2.11 M32 Starting Address Register</li> <li>4.4.2.13 CRW Base Address Register</li> <li>4.4.2.14 CRW Gathering Control Register</li> </ul>                               | 60<br>60<br>61<br>61<br>62<br>62<br>62<br>67<br>67<br>67<br>68<br>68<br>68<br>68<br>69<br>70<br>71<br>72<br>73<br>74<br>74<br>75<br>76<br>77             |

| <ul> <li>4.3.2.1 SCOM - HV Indirect Address Register</li> <li>4.3.2.2 SCOM HV Indirect Data Register</li> <li>4.3.2.3 SCOM Direct Mapped Registers</li> <li>4.4 ETU/RSB HV Registers</li> <li>4.4 ETU/RSB HV Register Address Map</li> <li>4.4.1 ETU/RSB HV Register Address Map</li> <li>4.4.2 Fundamental Register Set A</li> <li>4.4.2.1 LSI SourceID Register</li> <li>4.4.2.2 DMA Channel Status Register</li> <li>4.4.2.3 Processor Load/Store Status Register</li> <li>4.4.2.4 CONFIG_DATA Register</li> <li>4.4.2.5 Lock0 Register</li> <li>4.4.2.6 CONFIG_ADDRESS Register</li> <li>4.4.2.7 Lock1 Register</li> <li>4.4.2.8 PHB4 Configuration Register</li> <li>4.4.2.10 PELT-V Base Address Register</li> <li>4.4.2.11 M32 Starting Address Register</li> <li>4.4.2.12 PEST Base Address Register</li> <li>4.4.2.13 CRW Base Address Register</li> </ul> | 60<br>60<br>61<br>61<br>62<br>62<br>62<br>67<br>67<br>67<br>68<br>68<br>68<br>69<br>70<br>71<br>72<br>73<br>74<br>74<br>74<br>75<br>75<br>76<br>77<br>78 |

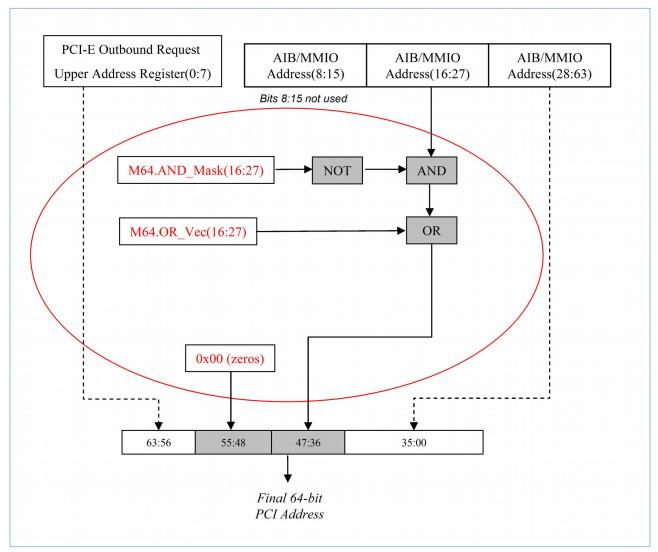

| 4.4.2.17 M64 Outbound Address AND/OR Mask Register (vA4.2) | . 80 |

|------------------------------------------------------------|------|

| 4.4.2.18 PCIe Outbound Request Upper Address Register      |      |

| 4.4.2.19 Non-Translate Prefix Register                     | . 82 |

| 4.4.2.20 DMA Read Sync Register                            | . 83 |

| 4.4.2.21 RTC Invalidate Register                           | . 84 |

| 4.4.2.22 TCE Kill Register                                 | . 85 |

| 4.4.2.23 Speculation Control Register                      | . 86 |

| 4.4.2.24 IODA Table Address Register                       | . 87 |

| 4.4.2.25 IODA Table Data Register                          | . 89 |

| 4.4.2.26 PHB4 General Capabilities Register                | 103  |

| 4.4.2.27 PHB4 TCE Capabilities Register                    | 104  |

| 4.4.2.28 PHB4 Interrupt Capabilities Register              | 105  |

| 4.4.2.29 PHB4 EEH Capabilities Register                    |      |

| 4.4.2.30 PAPR Error Injection Control Register             | 106  |

| 4.4.2.31 PAPR Error Injection Address Register             | 108  |

| 4.4.2.32 PAPR Error Injection Address Mask Register        | 108  |

| 4.4.2.33 ETU Error Summary Status Register                 | 109  |

| 4.4.2.34 Interrupt Notify Base Address Register            | 110  |

| 4.4.2.35 Interrupt Notify Base Index Register              | 110  |

| 4.4.3 Fundamental Register Set B                           | 111  |

| 4.4.3.1 PHB4 - Version Register                            | 111  |

| 4.4.3.2 PHB4 - Control Register                            | 111  |

| 4.4.3.3 PHB4 - AIB Fence Control Register                  | 114  |

| 4.4.3.4 PHB4 - TCE Tag Enable Register                     | 115  |

| 4.4.3.5 PHB4 - TCE Tag Watermark Register                  | 116  |

| 4.4.3.6 PHB4 - Timeout Control Register 1                  | 117  |

| 4.4.3.7 PHB4 - Timeout Control Register 2                  | 118  |

| 4.4.3.8 PHB4 - Quiesce DMA Register                        | 119  |

| 4.4.3.9 PHB4 - TCE Tag Status Register                     | 120  |

| 4.4.4 Error Registers                                      | 120  |

| 4.4.4.1 LEM FIR Accumulator Register                       | 120  |

| 4.4.4.2 LEM FIR AND Mask Register                          | 125  |

| 4.4.4.3 LEM FIR OR Mask Register                           | 126  |

| 4.4.4.4 LEM Error Mask Register                            |      |

| 4.4.4.5 LEM Error AND Mask Register                        | 127  |

| 4.4.4.6 LEM Error OR Mask Register                         | 128  |

| 4.4.4.7 LEM Action 0 Register                              | 128  |

| 4.4.4.8 LEM Action 1 Register                              | 129  |

| 4.4.4.9 LEM WOF Register                                   | 129  |

| 4.4.4.10 PHB4 Error Status Register                        | 130  |

| 4.4.4.11 PHB4 First Error Status Register                  |      |

| 4.4.4.12 PHB4 Error Injection Register                     | 132  |

| 4.4.4.13 PHB4 Error LEM Report Enable Register             | 133  |

| 4.4.4.14 PHB4 Error System Interrupt Enable Register       | 133  |

| 4.4.4.15 PHB4 Error EEH Freeze Enable Register             | 133  |

| 4.4.4.16 PHB4 Error AIB Fence Enable Register              | 134  |

| 4.4.4.17 PHB4 Error Log Register 0                         | 134  |

| 4.4.4.18 PHB4 Error Log Register 1                         | 134  |

| 4.4.4.19 PHB4 Error Status Mask Register                   |      |

| 4.4.4.20 PHB4 First Error Status Mask Register             | 135  |

|                                                            |      |

|    | 4.4.4.21 TXE Error Status Register                      | 1 | 36 |

|----|---------------------------------------------------------|---|----|

|    | 4.4.4.22 TXE First Error Status Register                |   |    |

|    | 4.4.4.23 TXE Error Injection Register                   |   |    |

|    | 4.4.4.24 TXE Error LEM Report Enable Register           |   |    |

|    | 4.4.4.25 TXE Error System Interrupt Enable Register     |   |    |

|    | 4.4.4.26 TXE Error EEH Freeze Enable Register           |   |    |

|    | 4.4.4.27 TXE Error AIB Fence Enable Register            |   |    |

|    | 4.4.4.27 TXE Error Log Register 0                       |   |    |

|    | 4.4.4.29 TXE Error Log Register 1                       |   |    |

|    | 4.4.4.29 TXE Error Status Mask Register                 |   |    |

|    | 4.4.4.30 TXE First Error Status Mask Register           |   |    |

|    |                                                         |   |    |

|    | 4.4.4.32 RXE_ARB Error Status Register                  |   |    |

|    | 4.4.4.33 RXE_ARB First Error Status Register            |   |    |

|    | 4.4.4.34 RXE_ARB Error Injection Register               |   |    |

|    | 4.4.4.35 RXE_ARB Error LEM Report Enable Register       |   |    |

|    | 4.4.4.36 RXE_ARB Error System Interrupt Enable Register |   |    |

|    | 4.4.4.37 RXE_ARB Error EEH Freeze Enable Register       |   |    |

|    | 4.4.4.38 RXE_ARB Error AIB Fence Enable Register        |   |    |

|    | 4.4.4.39 RXE_ARB Error Log Register 0                   |   |    |

|    | 4.4.4.40 RXE_ARB Error Log Register 1                   |   |    |

|    | 4.4.4.1 RXE_ARB Error Status Mask Register              |   |    |

|    | 4.4.42 RXE_ARB First Error Status Mask Register         |   |    |

|    | 4.4.43 RXE_MRG Error Status Register                    |   |    |

|    | 4.4.44 RXE_MRG First Error Status Register              |   |    |

|    | 4.4.45 RXE_MRG Error Injection Register                 |   |    |

|    | 4.4.4.46 RXE_MRG Error LEM Report Enable Register       |   |    |

|    | 4.4.4.47 RXE_MRG Error System Interrupt Enable Register |   |    |

|    | 4.4.4.48 RXE_MRG Error EEH Freeze Enable Register       |   |    |

|    | 4.4.4.49 RXE_MRG Error AIB Fence Enable Register        |   |    |

|    | 4.4.4.50 RXE_MRG Error Log Register 0                   |   |    |

|    | 4.4.4.51 RXE_MRG Error Log Register 1                   |   |    |

|    | 4.4.4.52 RXE_MRG Error Status Mask Register             |   |    |

|    | 4.4.4.53 RXE_MRG First Error Status Mask Register       |   |    |

|    | 4.4.4.54 RXE_TCE Error Status Register                  |   |    |

|    | 4.4.4.55 RXE_TCE First Error Status Register            | 1 | 61 |

|    | 4.4.4.56 RXE_TCE Error Injection Register               |   |    |

|    | 4.4.4.57 RXE_TCE Error LEM Report Enable Register       | 1 | 63 |

|    | 4.4.4.58 RXE_TCE Error System Interrupt Enable Register | 1 | 63 |

|    | 4.4.4.59 RXE_TCE Error EEH Freeze Enable Register       | 1 | 63 |

|    | 4.4.4.60 RXE_TCE Error AIB Fence Enable Register        | 1 | 64 |

|    | 4.4.4.61 RXE_TCE Error Log Register 0                   | 1 | 64 |

|    | 4.4.4.62 RXE_TCE Error Log Register 1                   | 1 | 64 |

|    | 4.4.4.63 RXE_TCE Error Status Mask Register             | 1 | 65 |

|    | 4.4.4.64 RXE_TCE First Error Status Mask Register       | 1 | 65 |

| 4. | 4.5 Debug Registers                                     |   |    |

|    | 4.4.5.1 PHB4 - Trace Control Register                   |   |    |

|    | 4.4.5.2 Performance Monitor Configuration Register      |   |    |

|    | 4.4.5.3 Performance Monitor Counter Register 0          |   |    |

|    | 4.4.5.4 Performance Monitor Counter Register 1          |   |    |

|    | 4.4.5.5 Performance Monitor Counter Register 2          |   |    |

|    | -                                                       |   |    |

| 4.4.5.6 Performance Monitor Counter Register 3 1                                    | 174 |

|-------------------------------------------------------------------------------------|-----|

| 4.5 PCI Configuration Space Registers 1                                             | 175 |

| 4.5.1 PCI Configuration Space Register Address Map 1                                | 175 |

| 4.5.2 PCI - Header Type-1 Registers (0x000 to 0x03C) 1                              |     |

| 4.5.2.1 PCI - Vendor ID/Device ID Register 1                                        | 179 |

| 4.5.2.2 PCI - Command/Status Register 1                                             | 180 |

| 4.5.2.3 PCI - Revision ID/Class Code Register 1                                     |     |

| 4.5.2.4 PCI - Cache Line Size, Master Latency, Header Type, BIST Register 1         |     |

| 4.5.2.5 PCI - Primary/Secondary/Subordinate Bus Number Register 1                   |     |

| 4.5.2.6 PCI - IO Base/Limit and Secondary Status Register                           |     |

| 4.5.2.7 PCI - Memory Base/Limit Register 1                                          | 184 |

| 4.5.2.8 PCI - Prefetch Base/Limit Register 1                                        |     |

| 4.5.2.9 PCI - Prefetch Base Upper Register 1                                        | 185 |

| 4.5.2.10 PCI - Prefetch Limit Upper Register 1                                      |     |

| 4.5.2.11 PCI - Capabilities Pointer Register 1                                      |     |

| 4.5.2.12 Bridge Control Register 1                                                  |     |

| 4.5.3 PM - Power Management Registers (0x040 to 0x044) 1                            | 188 |

| 4.5.3.1 PM - Capability ID/Next PTR/PMC Register                                    |     |

| 4.5.3.2 PM - PMCSR/PMCSR_BSE/Data Register 1                                        |     |

| 4.5.4 EC - PCI Express Capabilities Registers (0x048 to 0x078) 1                    |     |

| 4.5.4.1 EC - Capability ID/Next PTR/PCI Express Capabilities Register               | 190 |

| 4.5.4.2 EC - Device Capabilities Register 1                                         | 191 |

| 4.5.4.3 EC - Device Control/Status Register 1                                       |     |

| 4.5.4.4 EC - Link Capabilities Register 1                                           |     |

| 4.5.4.5 EC - Link Control/Status Register 1                                         | 196 |

| 4.5.4.6 EC - Slot Capabilities Register 1                                           | 198 |

| 4.5.4.7 EC - Slot Control/Status Register 2                                         | 201 |

| 4.5.4.8 EC - Root Control Register                                                  | 202 |

| 4.5.4.9 EC - Device Capabilities 2 Register 2                                       | 203 |

| 4.5.4.10 EC - Device Control/Status 2 Register 2                                    | 205 |

| 4.5.4.11 EC - Link Capabilities 2 Register 2                                        | 206 |

| 4.5.4.12 EC - Link Control/Status 2 Register 2                                      | 208 |

| 4.5.5 AER - Advanced Error Reporting Registers (0x100 to 0x144) 2                   | 213 |

| 4.5.5.1 AER - PCI Express Enhanced Capability Header 2                              | 213 |

| 4.5.5.2 AER - Uncorrectable Error Status Register 2                                 | 213 |

| 4.5.5.3 AER - Uncorrectable Error Mask Register 2                                   |     |

| 4.5.5.4 AER - Correctable Error Status Register 2                                   | 215 |

| 4.5.5.5 AER - Capabilities and Control Register 2                                   | 216 |

| 4.5.5.6 AER - Header Log Register #1 2                                              | 217 |

| 4.5.5.7 AER - Header Log Register #2 2                                              | 217 |

| 4.5.5.8 AER - Header Log Register #3 2                                              |     |

| 4.5.5.9 AER - Header Log Register #4 2                                              |     |

| 4.5.5.10 AER - Root Error Status Register 2                                         |     |

| 4.5.5.11 AER - Error Source Identification Register 2                               |     |

| 4.5.6 SEC - Secondary PCI Express Extended Capability Registers (0x148 to 0x170) 2  | 220 |

| 4.5.6.1 SEC - PCI Express Extended Capability Header Register 2                     | 220 |

| 4.5.6.2 SEC - Link Control 3 Register 2                                             |     |

| 4.5.7 P16 - Physical Layer 16 GT/s Extended Capability Registers (0x174 to 0x19C) 2 |     |

| 4.5.7.1 P16 - Physical Layer 16 GT/s Extended Capability Header Register 2          |     |

| 4.5.7.2 P16 - 16 GT/s Capabilities Register 2                                       | 221 |

| 4.5.7.3 P16 - 16 GT/s Control Register                                                    | 221 |

|-------------------------------------------------------------------------------------------|-----|

| 4.5.7.4 P16 - 16 GT/s Status Register                                                     |     |

| 4.5.7.5 P16 - 16 GT/s Local Data Parity Mismatch Status Register                          | 223 |

| 4.5.7.6 P16 - 16 GT/s First Retimer Data Parity Mismatch Status Register                  | 223 |

| 4.5.7.7 P16 - 16 GT/s Second Retimer Data Parity Mismatch Status Register                 | 224 |

| 4.5.8 LMR - Lane Margining at the Receiver Extended Capability Registers (0x1A0 to 0x1E4) | 224 |

| 4.5.8.1 LMR - Margining Extended Capability Header Register                               | 224 |

| 4.5.8.2 LMR - Margining Port Capabilities/Status Register                                 | 225 |

| 4.5.8.3 LMR - Margining Lane Control/Status Register # 1                                  | 226 |

| 4.5.8.4 LMR - Margining Lane Control/Status Register # 2                                  | 226 |

| 4.5.8.5 LMR - Margining Lane Control/Status Register # 3                                  | 227 |

| 4.5.8.6 LMR - Margining Lane Control/Status Register # 4                                  |     |

| 4.5.8.7 LMR - Margining Lane Control/Status Register # 5                                  |     |

| 4.5.8.8 LMR - Margining Lane Control/ Status Register # 6                                 |     |

| 4.5.8.9 LMR - Margining Lane Control/Status Register # 7                                  |     |

| 4.5.8.10 LMR - Margining Lane Control/Status Register # 8                                 |     |

| 4.5.8.11 LMR - Margining Lane Control/Status Register # 9                                 |     |

| 4.5.8.12 LMR - Margining Lane Control/Status Register # 10                                |     |

| 4.5.8.13 LMR - Margining Lane Control/Status Register # 11                                |     |

| 4.5.8.14 LMR - Margining Lane Control/Status Register # 12                                |     |

| 4.5.8.15 LMR - Margining Lane Control/Status Register # 13                                |     |

| 4.5.8.16 LMR - Margining Lane Control/Status Register # 14                                |     |

| 4.5.8.17 LMR - Margining Lane Control/Status Register # 15                                |     |

| 4.5.8.18 LMR - Margining Lane Control/Status Register # 16                                |     |

| 4.5.9 DLF - Data Link Feature Extended Capability Registers (0x1E8 to 0x1F0)              |     |

| 4.5.9.1 DLF - Data Link Feature Extended Capability Header Register                       |     |

| 4.5.9.2 DLF - Data Link Layer Capabilities Register                                       |     |

| 4.5.9.3 DLF - Data Link Feature Status Register                                           |     |

| 4.6 REGB Registers                                                                        |     |

| 4.6.1 REGB Internal Register Address Map                                                  |     |

| 4.6.2 PBL Core Registers                                                                  |     |

| 4.6.2.1 PBL - Control Register                                                            |     |

| 4.6.2.2 PBL - Timeout Control Register                                                    |     |

| 4.6.2.3 PBL - Nonposted Tag Enable Register                                               |     |

| 4.6.2.4 PBL - NBW Compare/Mask Register                                                   |     |

| 4.6.2.5 PBL - SYS_LINK_INIT Register                                                      |     |

| 4.6.2.6 PBL - Buffer Status Register                                                      |     |

| 4.6.2.7 PBL - Error Status Register                                                       |     |

| 4.6.2.8 PBL - First Error Status Register                                                 |     |

| •                                                                                         |     |

| 4.6.2.9 PBL - Error Injection Register                                                    |     |

| 4.6.2.10 PBL - Error INF Enable Register                                                  |     |

| 4.6.2.11 PBL - Error ERC Enable Register                                                  |     |

| 4.6.2.12 PBL - Error FAT Enable Register                                                  |     |

| 4.6.2.13 PBL - Error Log Register 0                                                       |     |

| 4.6.2.14 PBL - Error Log Register 1                                                       |     |

| 4.6.2.15 PBL - Error Status Mask Register                                                 |     |

| 4.6.2.16 PBL - First Error Status Mask Register                                           |     |

| 4.6.3 PCIe Stack Registers                                                                |     |

| 4.6.3.1 PCIe - System Configuration Register                                              |     |

| 4.6.3.2 PCIe - Bus Number Register                                                        | 256 |

| 4.6.3.3 PCIe - Core Reset Register                                         |       |

|----------------------------------------------------------------------------|-------|

| 4.6.3.4 PCIe - DLP Strapping Register                                      |       |

| 4.6.3.5 PCIe- Hot Plug Status Register                                     |       |

| 4.6.3.6 PCIe - Link Management Register                                    |       |

| 4.6.3.7 PCIe - DLP Training Control Register                               |       |

| 4.6.3.8 PCIe - DLP Loopback Status Register                                |       |

| 4.6.3.9 PCIe - DLP Fault Isolation Register                                |       |

| 4.6.3.10 PCIe - DLP Control Register                                       | . 265 |

| 4.6.3.11 PCIe - DLP Trace Read/Write Control Register                      | . 270 |

| 4.6.3.12 PCIe - DLP Trace Read Data Register                               | . 270 |

| 4.6.3.13 PCIe - DLP Error Log Register 1                                   | . 271 |

| 4.6.3.14 PCIe - DLP Error Log Register 2                                   | . 271 |

| 4.6.3.15 PCIe - DLP Error Status Register                                  | . 271 |

| 4.6.3.16 PCIe - DLP Error Counters Register                                | . 272 |

| 4.6.3.17 PCIe - DLP Error Injection Control Register                       | . 273 |

| 4.6.3.18 PCIe - DLP LANEEQCONTROL Register 0 (Gen 3, 8Gbps)                | . 275 |

| 4.6.3.19 PCIe - DLP LANEEQCONTROL Register 1 (Gen 3, 8Gbps)                |       |

| 4.6.3.20 PCIe - DLP LANEEQCONTROL Register 2 (Gen 3, 8Gbps)                |       |

| 4.6.3.21 PCIe - DLP LANEEQCONTROL Register 3 (Gen 3, 8Gbps)                | . 278 |

| 4.6.3.22 PCIe - DLP P1620-LANEEQCONTROL Register 0 (Gen 4, 16Gbps) (vA4.2) | . 279 |

| 4.6.3.23 PCIe - DLP P1620-LANEEQCONTROL Register 1 (Gen 4, 16Gbps) (vA4.2) |       |

| 4.6.3.24 PCIe - Trace Control Register                                     |       |

| 4.6.3.25 PCIe - Misc. Strapping Register                                   |       |