POWER9 PCIe Controller

**Functional Specification**

OpenPOWER

Version 1.1 27 July 2018

#### © Copyright International Business Machines Corporation 2018

Printed in the United States of America July 2018

IBM, the IBM logo, and ibm.com are trademarks or registered trademarks of International Business Machines Corp., registered in many jurisdictions worldwide. Other product and service names might be trademarks of IBM or other companies. A current list of IBM trademarks is available on the Web at "Copyright and trademark information" at <a href="http://www.ibm.com/legal/copytrade.shtml">www.ibm.com/legal/copytrade.shtml</a>.

The OpenPOWER word mark and the OpenPOWER logo mark, and related marks, are trademarks and service marks licensed by OpenPOWER.

Other company, product, and service names may be trademarks or service marks of others.

All information contained in this document is subject to change without notice. The products described in this document are NOT intended for use in applications such as implantation, life support, or other hazardous uses where malfunction could result in death, bodily injury, or catastrophic property damage. The information contained in this document does not affect or change IBM product specifications or warranties. Nothing in this document shall operate as an express or implied indemnity under the intellectual property rights of IBM or third parties. All information contained in this document was obtained in specific environments, and is presented as an illustration. The results obtained in other operating environments may vary.

This document is intended for the development of technology products compatible with Power Architecture®. You may use this document, for any purpose (commercial or personal) and make modifications and distribute; however, modifications to this document may violate Power Architecture and should be carefully considered. Any distribution of this document or its derivative works shall include this Notice page including but not limited to the IBM warranty disclaimer and IBM liability limitation. No other licenses (including patent licenses), expressed or implied, by estoppel or otherwise, to any intellectual property rights are granted by this document.

THE INFORMATION CONTAINED IN THIS DOCUMENT IS PROVIDED ON AN "AS IS" BASIS. IBM makes no representations or warranties, either express or implied, including but not limited to, warranties of merchantability, fitness for a particular purpose, or non-infringement, or that any practice or implementation of the IBM documentation will not infringe any third party patents, copyrights, trade secrets, or other rights. In no event will IBM be liable for damages arising directly or indirectly from any use of the information contained in this document.

IBM Systems 294 Route 100, Building SOM4 Somers, NY 10589-3216

The IBM home page can be found at ibm.com®.

Version 1.1 27 July 2018

# Contents

| List of Tables                                          | 7    |

|---------------------------------------------------------|------|

| List of Figures                                         | 9    |

| Revision Log                                            | 11   |

| About this Document                                     |      |

| Related Documents Conventions Used in this Document     |      |

|                                                         |      |

| 1. Overview                                             | 15   |

| 1.1 Description                                         | . 15 |

| 1.1.1 Processors Bus Common Queue (PBCQ)                | . 16 |

| 1.1.2 Processor Bus AIB interface (PBAIB)               | . 16 |

| 1.1.3 Express Transaction Unit                          | . 16 |

| 1.1.4 PCIe ASIC Intellectual Property                   |      |

| 1.1.5 Physical Coding Sublayer                          |      |

| 1.1.6 Physical Media Access                             | . 17 |

| 1.2 POWER9 Configurations                               | . 17 |

| 1.3 Reliability, Availability, and Serviceability (RAS) |      |

| 1.3.1 Bit-Level RAS                                     |      |

| 1.3.2 Enhanced Error Handling (EEH)                     | . 19 |

| 1.3.3 Freeze Mode                                       | . 19 |

|                                                         |      |

| 2. Processor Bus Common Queue                           | 20   |

| 2.1 I/O Mode Features                                   | . 20 |

| 2.2 CAPP Mode Features                                  |      |

| 2.3 PBCQ Outbound Interface                             |      |

| 2.3.1 Outbound Ordering Rules                           |      |

| 2.3.2 Outbound SMP Interconnect Tag Identifiers         |      |

| 2.4 Outbound Operation Summary                          |      |

| 2.4 Outbound Operation Summary                          |      |

| 2.4.2 Cache-Inhibited Write and Peer-to-Peer Write      |      |

| 2.4.2 Cache-Infinited Write and Feel-10-Feel Write      |      |

| 2.4.4 APC Master Reads                                  |      |

|                                                         |      |

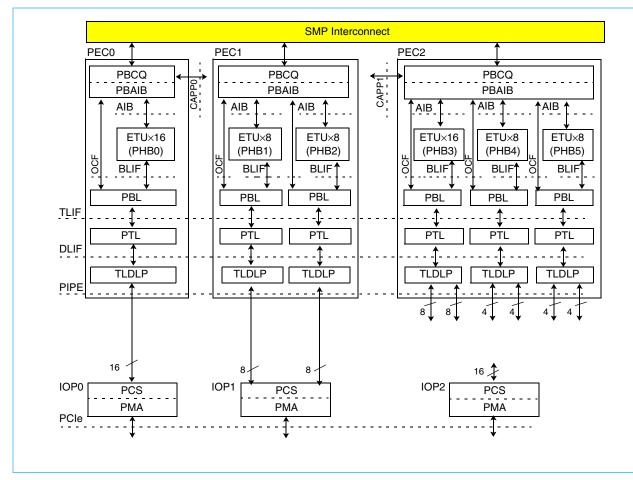

| 2.5 Outbound Data Flow Diagram                          |      |

| 2.6 PBCQ Inbound Interface                              |      |

| 2.7 Inbound Ordering Rules                              |      |

| 2.7.1 PCIe-Only Mode                                    |      |

| 2.7.2 CAPP Mode                                         |      |

| 2.8 Command Scope                                       |      |

| 2.9 Inbound Transaction Identifiers                     |      |

| 2.10 DMA Write Cache Inject Mode                        | . 29 |

| 2.11 Inbound Operations Summary                         | . 30 |

| 2.11.1 DMA Read                                         | . 30 |

|    | 2.11.2 DMA Write                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                           |

|----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|

|    | 2.11.3 Interrupt Notify                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                           |

|    | 2.11.4 Inbound CAPP Write                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                           |

|    | 2.12 Inbound Data Flow Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                           |

|    | 2.13 Peer-to-Peer Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                           |

|    | 2.13.1 Outbound Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                           |

|    | 2.14 PBCQ Error Handling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                           |

|    | 2.14.1 PBCQ Freeze Behavior                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                           |

|    | 2.14.2 PHB EEH Support                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                           |

|    | 2.14.3 PBCQ SMP Interconnect Hang Behavior                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 34                                                                                                                                        |

| 3. | Tunnel Operations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 35                                                                                                                                        |

| 0. | 3.1 ASB Notify                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                           |

|    | 3.2 Atomics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                           |

|    | 5.2 AUTILICS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 39                                                                                                                                        |

| 4. | PBCQ CAPP Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 42                                                                                                                                        |

|    | 4.1 CAPP Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                           |

|    | 4.1.1 Inbound CAPP Traffic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 42                                                                                                                                        |

|    | 4.1.2 Outbound CAPP Traffic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 42                                                                                                                                        |

|    | 4.2 Special CAPP Modes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 42                                                                                                                                        |

|    | 4.2.1 Non-Blocking Write                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                           |

|    | 4.2.2 NMMU Packets                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 43                                                                                                                                        |

| F  | Processor Bus Common Queue Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 45                                                                                                                                        |

| э. | Processor bus Common Queue Bedisiers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 40                                                                                                                                        |

|    | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                           |

|    | 5.1 Processor Bus Common Queue Registers Descriptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 47                                                                                                                                        |

|    | 5.1 Processor Bus Common Queue Registers Descriptions<br>5.1.1 PBCQ Hardware Configuration Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 47<br>47                                                                                                                                  |

|    | 5.1 Processor Bus Common Queue Registers Descriptions<br>5.1.1 PBCQ Hardware Configuration Register<br>5.1.2 Drop Priority Control Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 47<br>47<br>51                                                                                                                            |

|    | <ul> <li>5.1 Processor Bus Common Queue Registers Descriptions</li> <li>5.1.1 PBCQ Hardware Configuration Register</li> <li>5.1.2 Drop Priority Control Register</li> <li>5.1.3 PBCQ Error Inject Control Register</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 47<br>47<br>51<br>52                                                                                                                      |

|    | <ul> <li>5.1 Processor Bus Common Queue Registers Descriptions</li> <li>5.1.1 PBCQ Hardware Configuration Register</li> <li>5.1.2 Drop Priority Control Register</li> <li>5.1.3 PBCQ Error Inject Control Register</li> <li>5.1.4 PCI Nest Clock Trace Control Register</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 47<br>47<br>51<br>52<br>53                                                                                                                |

|    | <ul> <li>5.1 Processor Bus Common Queue Registers Descriptions</li> <li>5.1.1 PBCQ Hardware Configuration Register</li> <li>5.1.2 Drop Priority Control Register</li> <li>5.1.3 PBCQ Error Inject Control Register</li> <li>5.1.4 PCI Nest Clock Trace Control Register</li> <li>5.1.5 PBCQ Performance Monitor Control Register</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 47<br>47<br>51<br>52<br>53<br>57                                                                                                          |

|    | <ul> <li>5.1 Processor Bus Common Queue Registers Descriptions</li> <li>5.1.1 PBCQ Hardware Configuration Register</li> <li>5.1.2 Drop Priority Control Register</li> <li>5.1.3 PBCQ Error Inject Control Register</li> <li>5.1.4 PCI Nest Clock Trace Control Register</li> <li>5.1.5 PBCQ Performance Monitor Control Register</li> <li>5.1.6 PBCQ Processor Bus Address Extension Mask</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 47<br>47<br>51<br>52<br>53<br>57<br>59                                                                                                    |

|    | <ul> <li>5.1 Processor Bus Common Queue Registers Descriptions</li> <li>5.1.1 PBCQ Hardware Configuration Register</li> <li>5.1.2 Drop Priority Control Register</li> <li>5.1.3 PBCQ Error Inject Control Register</li> <li>5.1.4 PCI Nest Clock Trace Control Register</li> <li>5.1.5 PBCQ Performance Monitor Control Register</li> <li>5.1.6 PBCQ Processor Bus Address Extension Mask</li> <li>5.1.7 PBCQ Predictive Vector Timeout Register</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 47<br>51<br>52<br>53<br>57<br>59<br>60                                                                                                    |

|    | <ul> <li>5.1 Processor Bus Common Queue Registers Descriptions</li> <li>5.1.1 PBCQ Hardware Configuration Register</li> <li>5.1.2 Drop Priority Control Register</li> <li>5.1.3 PBCQ Error Inject Control Register</li> <li>5.1.4 PCI Nest Clock Trace Control Register</li> <li>5.1.5 PBCQ Performance Monitor Control Register</li> <li>5.1.6 PBCQ Processor Bus Address Extension Mask</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 47<br>47<br>51<br>52<br>53<br>57<br>59<br>60<br>61                                                                                        |

|    | <ul> <li>5.1 Processor Bus Common Queue Registers Descriptions</li> <li>5.1.1 PBCQ Hardware Configuration Register</li> <li>5.1.2 Drop Priority Control Register</li> <li>5.1.3 PBCQ Error Inject Control Register</li> <li>5.1.4 PCI Nest Clock Trace Control Register</li> <li>5.1.5 PBCQ Performance Monitor Control Register</li> <li>5.1.6 PBCQ Processor Bus Address Extension Mask</li> <li>5.1.7 PBCQ Predictive Vector Timeout Register</li> <li>5.1.8 CAPP Control Register</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 47<br>47<br>51<br>52<br>53<br>57<br>59<br>60<br>61<br>61                                                                                  |

|    | <ul> <li>5.1 Processor Bus Common Queue Registers Descriptions</li> <li>5.1.1 PBCQ Hardware Configuration Register</li> <li>5.1.2 Drop Priority Control Register</li> <li>5.1.3 PBCQ Error Inject Control Register</li> <li>5.1.4 PCI Nest Clock Trace Control Register</li> <li>5.1.5 PBCQ Performance Monitor Control Register</li> <li>5.1.6 PBCQ Processor Bus Address Extension Mask</li> <li>5.1.7 PBCQ Predictive Vector Timeout Register</li> <li>5.1.8 CAPP Control Register</li> <li>5.1.9 PBCQ Read Stack Override Register</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 47<br>47<br>51<br>52<br>53<br>57<br>59<br>60<br>61<br>61<br>62                                                                            |

|    | <ul> <li>5.1 Processor Bus Common Queue Registers Descriptions</li> <li>5.1.1 PBCQ Hardware Configuration Register</li> <li>5.1.2 Drop Priority Control Register</li> <li>5.1.3 PBCQ Error Inject Control Register</li> <li>5.1.4 PCI Nest Clock Trace Control Register</li> <li>5.1.5 PBCQ Performance Monitor Control Register</li> <li>5.1.6 PBCQ Processor Bus Address Extension Mask</li> <li>5.1.7 PBCQ Predictive Vector Timeout Register</li> <li>5.1.8 CAPP Control Register</li> <li>5.1.9 PBCQ Read Stack Override Register</li> <li>5.1.10 PBCQ Write Stack Override Register</li> <li>5.1.11 PBCQ Store Stack Override Register</li> <li>5.1.12 PBCQ Retry Backoff Control Register</li> </ul>                                                                                                                                                                                                                                                                                                                                                                  | 47<br>47<br>51<br>52<br>53<br>57<br>59<br>60<br>61<br>61<br>62<br>62<br>63                                                                |

|    | <ul> <li>5.1 Processor Bus Common Queue Registers Descriptions</li> <li>5.1.1 PBCQ Hardware Configuration Register</li> <li>5.1.2 Drop Priority Control Register</li> <li>5.1.3 PBCQ Error Inject Control Register</li> <li>5.1.4 PCI Nest Clock Trace Control Register</li> <li>5.1.5 PBCQ Performance Monitor Control Register</li> <li>5.1.6 PBCQ Processor Bus Address Extension Mask</li> <li>5.1.7 PBCQ Predictive Vector Timeout Register</li> <li>5.1.8 CAPP Control Register</li> <li>5.1.9 PBCQ Read Stack Override Register</li> <li>5.1.10 PBCQ Write Stack Override Register</li> <li>5.1.11 PBCQ Store Stack Override Register</li> <li>5.1.12 PBCQ Retry Backoff Control Register</li> <li>5.1.13 PCI Nest Fault Isolation Register (FIR), Clear, Set</li> </ul>                                                                                                                                                                                                                                                                                              | 47<br>47<br>51<br>52<br>53<br>57<br>59<br>60<br>61<br>61<br>62<br>63<br>63<br>64                                                          |

|    | <ul> <li>5.1 Processor Bus Common Queue Registers Descriptions</li> <li>5.1.1 PBCQ Hardware Configuration Register</li> <li>5.1.2 Drop Priority Control Register</li> <li>5.1.3 PBCQ Error Inject Control Register</li> <li>5.1.4 PCI Nest Clock Trace Control Register</li> <li>5.1.5 PBCQ Performance Monitor Control Register</li> <li>5.1.6 PBCQ Processor Bus Address Extension Mask</li> <li>5.1.7 PBCQ Predictive Vector Timeout Register</li> <li>5.1.8 CAPP Control Register</li> <li>5.1.9 PBCQ Read Stack Override Register</li> <li>5.1.10 PBCQ Write Stack Override Register</li> <li>5.1.11 PBCQ Store Stack Override Register</li> <li>5.1.12 PBCQ Retry Backoff Control Register</li> <li>5.1.13 PCI Nest Fault Isolation Register (FIR), Clear, Set</li> <li>5.1.14 PCI Nest FIR Action 0</li> </ul>                                                                                                                                                                                                                                                        | 47<br>47<br>51<br>52<br>53<br>57<br>59<br>60<br>61<br>61<br>62<br>62<br>63<br>64<br>66                                                    |

|    | <ul> <li>5.1 Processor Bus Common Queue Registers Descriptions</li> <li>5.1.1 PBCQ Hardware Configuration Register</li> <li>5.1.2 Drop Priority Control Register</li> <li>5.1.3 PBCQ Error Inject Control Register</li> <li>5.1.4 PCI Nest Clock Trace Control Register</li> <li>5.1.5 PBCQ Performance Monitor Control Register</li> <li>5.1.6 PBCQ Processor Bus Address Extension Mask</li> <li>5.1.7 PBCQ Predictive Vector Timeout Register</li> <li>5.1.8 CAPP Control Register</li> <li>5.1.9 PBCQ Read Stack Override Register</li> <li>5.1.10 PBCQ Write Stack Override Register</li> <li>5.1.11 PBCQ Store Stack Override Register</li> <li>5.1.12 PBCQ Retry Backoff Control Register</li> <li>5.1.13 PCI Nest Fault Isolation Register (FIR), Clear, Set</li> <li>5.1.15 PCI Nest FIR Action 0</li> <li>5.1.15 PCI Nest FIR Action 1</li> </ul>                                                                                                                                                                                                                  | 47<br>47<br>51<br>52<br>53<br>57<br>59<br>60<br>61<br>61<br>62<br>62<br>63<br>64<br>66<br>67                                              |

|    | <ul> <li>5.1 Processor Bus Common Queue Registers Descriptions</li> <li>5.1.1 PBCQ Hardware Configuration Register</li> <li>5.1.2 Drop Priority Control Register</li> <li>5.1.3 PBCQ Error Inject Control Register</li> <li>5.1.4 PCI Nest Clock Trace Control Register</li> <li>5.1.5 PBCQ Performance Monitor Control Register</li> <li>5.1.6 PBCQ Processor Bus Address Extension Mask</li> <li>5.1.7 PBCQ Predictive Vector Timeout Register</li> <li>5.1.8 CAPP Control Register</li> <li>5.1.9 PBCQ Read Stack Override Register</li> <li>5.1.10 PBCQ Write Stack Override Register</li> <li>5.1.11 PBCQ Store Stack Override Register</li> <li>5.1.12 PBCQ Retry Backoff Control Register</li> <li>5.1.13 PCI Nest Fault Isolation Register (FIR), Clear, Set</li> <li>5.1.14 PCI Nest FIR Action 0</li> <li>5.1.15 PCI Nest FIR Mask, Clear, Set</li> </ul>                                                                                                                                                                                                          | $\begin{array}{r} 47\\ 47\\ 51\\ 52\\ 53\\ 57\\ 59\\ 60\\ 61\\ 61\\ 62\\ 63\\ 64\\ 66\\ 67\\ 68\\ \end{array}$                            |

|    | <ul> <li>5.1 Processor Bus Common Queue Registers Descriptions</li> <li>5.1.1 PBCQ Hardware Configuration Register</li> <li>5.1.2 Drop Priority Control Register</li> <li>5.1.3 PBCQ Error Inject Control Register</li> <li>5.1.4 PCI Nest Clock Trace Control Register</li> <li>5.1.5 PBCQ Performance Monitor Control Register</li> <li>5.1.6 PBCQ Processor Bus Address Extension Mask</li> <li>5.1.7 PBCQ Predictive Vector Timeout Register</li> <li>5.1.8 CAPP Control Register</li> <li>5.1.9 PBCQ Read Stack Override Register</li> <li>5.1.10 PBCQ Write Stack Override Register</li> <li>5.1.11 PBCQ Store Stack Override Register</li> <li>5.1.12 PBCQ Retry Backoff Control Register</li> <li>5.1.13 PCI Nest Fault Isolation Register (FIR), Clear, Set</li> <li>5.1.15 PCI Nest FIR Action 1</li> <li>5.1.16 PCI Nest FIR Mask, Clear, Set</li> <li>5.1.17 PCI Nest FIR WOF</li> </ul>                                                                                                                                                                         | $\begin{array}{r} 47\\ 47\\ 51\\ 52\\ 53\\ 57\\ 59\\ 60\\ 61\\ 62\\ 62\\ 63\\ 64\\ 66\\ 67\\ 68\\ 68\\ 68\end{array}$                     |

|    | <ul> <li>5.1 Processor Bus Common Queue Registers Descriptions</li> <li>5.1.1 PBCQ Hardware Configuration Register</li> <li>5.1.2 Drop Priority Control Register</li> <li>5.1.3 PBCQ Error Inject Control Register</li> <li>5.1.4 PCI Nest Clock Trace Control Register</li> <li>5.1.5 PBCQ Performance Monitor Control Register</li> <li>5.1.6 PBCQ Processor Bus Address Extension Mask</li> <li>5.1.7 PBCQ Predictive Vector Timeout Register</li> <li>5.1.8 CAPP Control Register</li> <li>5.1.10 PBCQ Read Stack Override Register</li> <li>5.1.11 PBCQ Store Stack Override Register</li> <li>5.1.12 PBCQ Retry Backoff Control Register</li> <li>5.1.13 PCI Nest Fla Action 0</li> <li>5.1.15 PCI Nest Fla Action 1</li> <li>5.1.16 PCI Nest Fla Mask, Clear, Set</li> <li>5.1.17 PCI Nest Fla WOF</li> <li>5.1.18 Error Report Register 0</li> </ul>                                                                                                                                                                                                                 | $\begin{array}{r} 47\\ 47\\ 51\\ 52\\ 53\\ 57\\ 59\\ 60\\ 61\\ 61\\ 62\\ 63\\ 64\\ 66\\ 67\\ 68\\ 68\\ 69\\ \end{array}$                  |

|    | <ul> <li>5.1 Processor Bus Common Queue Registers Descriptions</li> <li>5.1.1 PBCQ Hardware Configuration Register</li> <li>5.1.2 Drop Priority Control Register</li> <li>5.1.3 PBCQ Error Inject Control Register</li> <li>5.1.4 PCI Nest Clock Trace Control Register</li> <li>5.1.5 PBCQ Performance Monitor Control Register</li> <li>5.1.6 PBCQ Processor Bus Address Extension Mask</li> <li>5.1.7 PBCQ Predictive Vector Timeout Register</li> <li>5.1.8 CAPP Control Register</li> <li>5.1.9 PBCQ Read Stack Override Register</li> <li>5.1.10 PBCQ Write Stack Override Register</li> <li>5.1.11 PBCQ Store Stack Override Register</li> <li>5.1.12 PBCQ Retry Backoff Control Register</li> <li>5.1.13 PCI Nest Fla Action 0</li> <li>5.1.15 PCI Nest FIR Action 1</li> <li>5.1.16 PCI Nest FIR Mask, Clear, Set</li> <li>5.1.17 PCI Nest FIR Mask, Clear, Set</li> <li>5.1.17 PCI Nest FIR WOF</li> <li>5.1.18 Error Report Register 0</li> <li>5.1.19 Error Report Register 1</li> </ul>                                                                         | $\begin{array}{r} 47\\ 47\\ 51\\ 52\\ 53\\ 57\\ 59\\ 60\\ 61\\ 61\\ 62\\ 63\\ 64\\ 66\\ 67\\ 68\\ 68\\ 69\\ 71\\ \end{array}$             |

|    | <ul> <li>5.1 Processor Bus Common Queue Registers Descriptions</li> <li>5.1.1 PBCQ Hardware Configuration Register</li> <li>5.1.2 Drop Priority Control Register</li> <li>5.1.3 PBCQ Error Inject Control Register</li> <li>5.1.4 PCI Nest Clock Trace Control Register</li> <li>5.1.5 PBCQ Performance Monitor Control Register</li> <li>5.1.6 PBCQ Processor Bus Address Extension Mask</li> <li>5.1.7 PBCQ Predictive Vector Timeout Register</li> <li>5.1.8 CAPP Control Register</li> <li>5.1.9 PBCQ Read Stack Override Register</li> <li>5.1.10 PBCQ Write Stack Override Register</li> <li>5.1.12 PBCQ Retry Backoff Control Register</li> <li>5.1.12 PBCQ Retry Backoff Control Register</li> <li>5.1.13 PCI Nest FIR Action 0</li> <li>5.1.15 PCI Nest FIR Action 1</li> <li>5.1.16 PCI Nest FIR Mask, Clear, Set</li> <li>5.1.17 PCI Nest FIR Moor</li> <li>5.1.18 Error Report Register 0</li> <li>5.1.20 PBCQ General Status Register</li> </ul>                                                                                                                | $\begin{array}{c} 47\\ 47\\ 51\\ 52\\ 53\\ 57\\ 59\\ 60\\ 61\\ 62\\ 63\\ 64\\ 66\\ 67\\ 68\\ 68\\ 69\\ 71\\ 72\\ \end{array}$             |

|    | <ul> <li>5.1 Processor Bus Common Queue Registers Descriptions</li> <li>5.1.1 PBCQ Hardware Configuration Register</li> <li>5.1.2 Drop Priority Control Register</li> <li>5.1.3 PBCQ Error Inject Control Register</li> <li>5.1.4 PCI Nest Clock Trace Control Register</li> <li>5.1.5 PBCQ Performance Monitor Control Register</li> <li>5.1.6 PBCQ Processor Bus Address Extension Mask</li> <li>5.1.7 PBCQ Predictive Vector Timeout Register</li> <li>5.1.8 CAPP Control Register</li> <li>5.1.9 PBCQ Read Stack Override Register</li> <li>5.1.10 PBCQ Write Stack Override Register</li> <li>5.1.12 PBCQ Retry Backoff Control Register</li> <li>5.1.13 PCI Nest Fault Isolation Register (FIR), Clear, Set</li> <li>5.1.14 PCI Nest FIR Action 0</li> <li>5.1.15 PCI Nest FIR Mask, Clear, Set</li> <li>5.1.17 PCI Nest FIR Mask, Clear, Set</li> <li>5.1.18 Error Report Register 0</li> <li>5.1.20 PBCQ General Status Register</li> <li>5.1.21 PBCQ Mode Register</li> </ul>                                                                                       | $\begin{array}{c} 47\\ 47\\ 51\\ 52\\ 53\\ 57\\ 59\\ 60\\ 61\\ 62\\ 62\\ 63\\ 64\\ 66\\ 67\\ 68\\ 69\\ 71\\ 72\\ 72\\ 72\end{array}$      |

|    | <ul> <li>5.1 Processor Bus Common Queue Registers Descriptions</li> <li>5.1.1 PBCQ Hardware Configuration Register</li> <li>5.1.2 Drop Priority Control Register</li> <li>5.1.3 PBCQ Error Inject Control Register</li> <li>5.1.4 PCI Nest Clock Trace Control Register</li> <li>5.1.5 PBCQ Performance Monitor Control Register</li> <li>5.1.6 PBCQ Processor Bus Address Extension Mask</li> <li>5.1.7 PBCQ Predictive Vector Timeout Register</li> <li>5.1.8 CAPP Control Register</li> <li>5.1.9 PBCQ Read Stack Override Register</li> <li>5.1.10 PBCQ Write Stack Override Register</li> <li>5.1.11 PBCQ Store Stack Override Register</li> <li>5.1.12 PBCQ Retry Backoff Control Register</li> <li>5.1.13 PCI Nest Fault Isolation Register (FIR), Clear, Set</li> <li>5.1.14 PCI Nest FIR Action 1</li> <li>5.1.15 PCI Nest FIR Mask, Clear, Set</li> <li>5.1.17 PCI Nest FIR Mask, Clear, Set</li> <li>5.1.18 Error Report Register 0</li> <li>5.1.20 PBCQ General Status Register</li> <li>5.1.21 PBCQ Mode Register</li> <li>5.1.21 PBCQ Mode Register</li> </ul> | $\begin{array}{c} 47\\ 47\\ 51\\ 52\\ 53\\ 57\\ 59\\ 60\\ 61\\ 62\\ 63\\ 64\\ 66\\ 67\\ 68\\ 68\\ 69\\ 71\\ 72\\ 72\\ 72\\ 72\end{array}$ |

|    | <ul> <li>5.1 Processor Bus Common Queue Registers Descriptions</li> <li>5.1.1 PBCQ Hardware Configuration Register</li> <li>5.1.2 Drop Priority Control Register</li> <li>5.1.3 PBCQ Error Inject Control Register</li> <li>5.1.4 PCI Nest Clock Trace Control Register</li> <li>5.1.5 PBCQ Performance Monitor Control Register</li> <li>5.1.6 PBCQ Processor Bus Address Extension Mask</li> <li>5.1.7 PBCQ Predictive Vector Timeout Register</li> <li>5.1.8 CAPP Control Register</li> <li>5.1.9 PBCQ Read Stack Override Register</li> <li>5.1.10 PBCQ Write Stack Override Register</li> <li>5.1.12 PBCQ Retry Backoff Control Register</li> <li>5.1.13 PCI Nest Fault Isolation Register (FIR), Clear, Set</li> <li>5.1.14 PCI Nest FIR Action 0</li> <li>5.1.15 PCI Nest FIR Mask, Clear, Set</li> <li>5.1.17 PCI Nest FIR Mask, Clear, Set</li> <li>5.1.18 Error Report Register 0</li> <li>5.1.20 PBCQ General Status Register</li> <li>5.1.21 PBCQ Mode Register</li> </ul>                                                                                       | $\begin{array}{c} 47\\ 47\\ 51\\ 52\\ 53\\ 57\\ 59\\ 60\\ 61\\ 62\\ 63\\ 64\\ 66\\ 67\\ 68\\ 68\\ 69\\ 71\\ 72\\ 72\\ 72\\ 73\end{array}$ |

| 5.1.25 MMIO Base Address Register Mask 1               | 74 |

|--------------------------------------------------------|----|

| 5.1.26 PHB Register Base Address Register              | 74 |

| 5.1.27 Interrupt Base Address Register                 |    |

| 5.1.28 Base Address Enable Register                    |    |

| 5.1.29 Data Freeze Type Register                       |    |

| 5.1.30 PBCQ Tunnel Bar Register                        |    |

| 5.1.31 PBAIB Hardware Control Register                 |    |

| 5.1.32 PCIe Read Stack Override Register Copy          |    |

| 5.1.33 PCI Fault Isolation Register (PFIR), Clear, Set |    |

| 5.1.34 PCI FIR Action 0                                |    |

| 5.1.35 PCI FIR Action 1                                |    |

| 5.1.36 PCI FIR Mask, Clear, Set                        |    |

| 5.1.37 PCI FIR WOF                                     |    |

| 5.1.38 ETU Reset Register                              |    |

| 5.1.39 PBAIB Error Report Register                     |    |

| 5.1.40 PBAIB TX Command Credit Register                |    |

| 5.1.41 PBAIB TX Data Credit Register                   | 85 |

|                                                        | 07 |

| 6. IOP-to-PE Unit Connectivity                         |    |

| 6.1 PHB Board Wiring Combinations                      | 88 |

|                                                        |    |

| 7. Error Handling                                      |    |

| 7.1 Recovery Classes                                   |    |

| 7.1.1 INF Class Error Handling                         |    |

| 7.1.2 Freeze Class Error Handling                      |    |

| 7.1.3 Checkstop Class Error Handling                   |    |

| 7.2 Error Recovery                                     |    |

| 7.2.1 Recovery Sequences                               |    |

| 7.2.1.1 INF Class                                      |    |

| 7.2.1.2 Freeze Class                                   |    |

| 7.2.1.3 Checkstop Class                                |    |

| 7.2.1.4 Memory Preserving IPL                          | 96 |

| 8. PEC Verification Register Initialization            | 07 |

| -                                                      |    |

| 8.1 PEC Verification Initialization Sequence           | 97 |

| Glossary                                               | 99 |

|                                                        |    |

## **List of Tables**

| Table 2-1.  | PBCQ I/O Mode Default Resource Allocation by Stack   | 21 |

|-------------|------------------------------------------------------|----|

| Table 2-2.  | PBCQ CAPP Mode Resource Allocation by Stack          | 22 |

| Table 2-3.  | Outbound SMP interconnect Reflected Command Summary  | 22 |

| Table 2-4.  | Outbound Ordering Rules                              | 23 |

| Table 2-5.  | PEC Acknowledge Tag Definition                       | 23 |

| Table 2-6.  | PEC Route Tag Definition                             | 23 |

| Table 2-7.  | Inbound SMP Interconnect Command Summary             | 27 |

| Table 2-8.  | Inbound Order Rules                                  | 28 |

| Table 2-9.  | Minimum Command Scope                                | 29 |

| Table 2-10. | PEC Transaction ID Definition                        | 29 |

| Table 2-11. | PEC Bus Master Command Hang Behavior                 | 34 |

| Table 2-12. | PEC Data Hang Behavior                               | 34 |

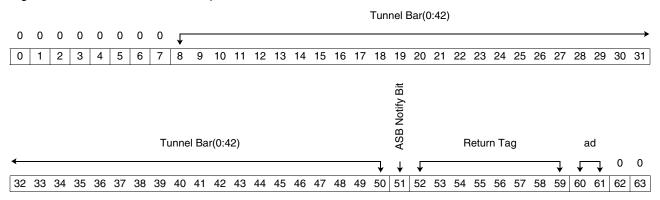

| Table 3-1.  | Tunnel Metadata Field                                | 35 |

| Table 3-2.  | Tunnel Response Address                              | 36 |

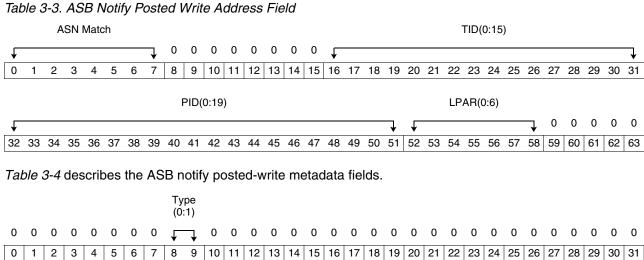

| Table 3-3.  | ASB Notify Posted Write Address Field                | 37 |

| Table 3-4.  | ASB Notify Posted Write Metadata                     | 37 |

| Table 3-5.  | ASB Notify Response Address                          | 38 |

| Table 3-6.  | ASB Notify Response Data                             | 38 |

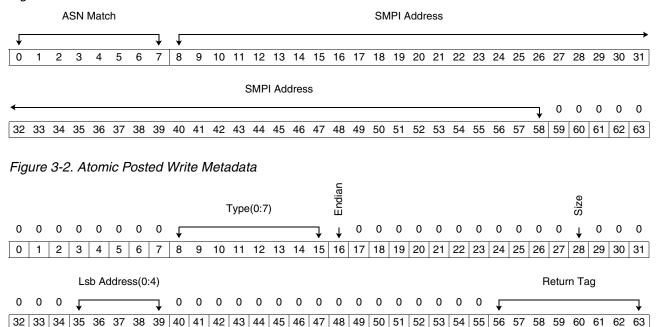

| Table 3-7.  | Atomic Posted Write Metadata                         | 39 |

| Table 3-8.  | Atomic Type                                          | 40 |

| Table 3-9.  | Alignment of 16-Byte Data for Atomic Posted Write    | 40 |

| Table 3-10. | Atomic with Fetch Response Address                   | 41 |

| Table 5-1.  | PBCQ Register Summary                                | 45 |

| Table 5-2.  | Register Access Legend                               | 47 |

| Table 5-3.  | Performance Monitor Group Definition                 | 58 |

| Table 6-1.  | IOP - PHB Assignments                                | 87 |

| Table 6-2.  | PHB Lane Configuration and Swap Bit Register Mapping | 88 |

| Table 6-3.  | PHB0 Wiring Combinations                             | 88 |

| Table 6-4.  | PHB1 Wiring Combinations                             | 88 |

| Table 6-5.  | PHB2 Wiring Combinations                             | 89 |

| Table 6-6.  | PHB3 Wiring Combinations                             | 89 |

| Table 6-7.  | PHB4 Wiring Combinations                             | 90 |

| Table 6-8.  | PHB5 Wiring Combinations                             | 91 |

| Table 7-1.  | INF Recovery Sequence                                | 94 |

| Table 7-2.  | Freeze Recovery Sequence                             | 95 |

| Table 7-3.  | Memory Preserving IPL Recover Sequence               | 96 |

| Table 8-1.  | PEC Initialization Sequence                          | 97 |

# List of Figures

| High-Level Block Diagram                            | 15                                                                                                                                                                                                                                                                                                                                            |

|-----------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| POWER9 PCIe High-Level Diagram                      | 18                                                                                                                                                                                                                                                                                                                                            |

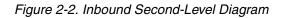

| Outbound Second-Level Diagram                       | 26                                                                                                                                                                                                                                                                                                                                            |

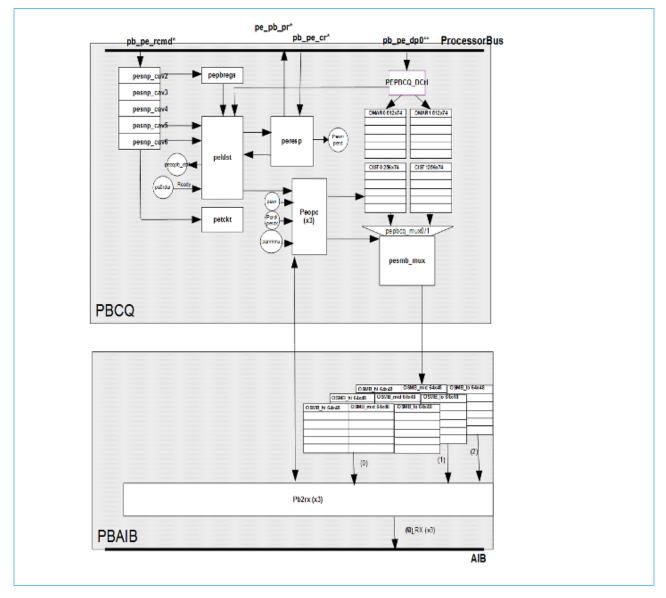

| Inbound Second-Level Diagram                        | 32                                                                                                                                                                                                                                                                                                                                            |

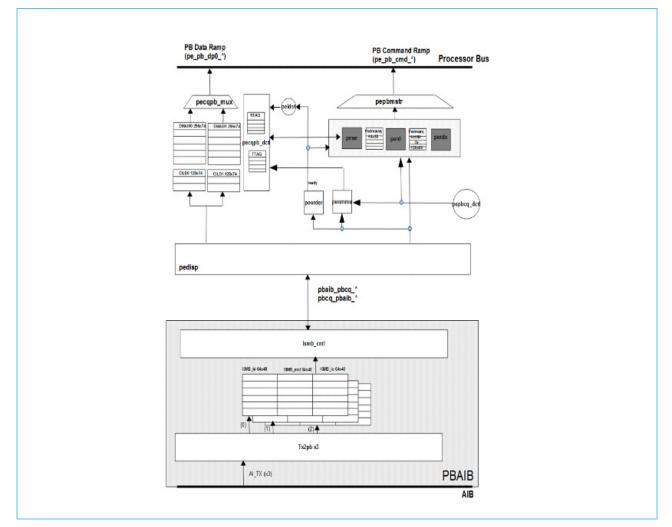

| Atomic Posted Write Address Field                   | 39                                                                                                                                                                                                                                                                                                                                            |

| Atomic Posted Write Metadata                        | 39                                                                                                                                                                                                                                                                                                                                            |

| Atomic with Fetch Response Address                  | 41                                                                                                                                                                                                                                                                                                                                            |

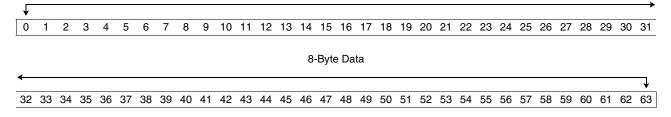

| Atomic Response Data (4-Byte Data)                  | 41                                                                                                                                                                                                                                                                                                                                            |

| Atomic Response Data (8-Byte Data)                  | 41                                                                                                                                                                                                                                                                                                                                            |

| CAPI NMMU Request Address Format (Checkout Request) | 43                                                                                                                                                                                                                                                                                                                                            |

| CAPI NMMU Request Address Format (Response Request) | 43                                                                                                                                                                                                                                                                                                                                            |

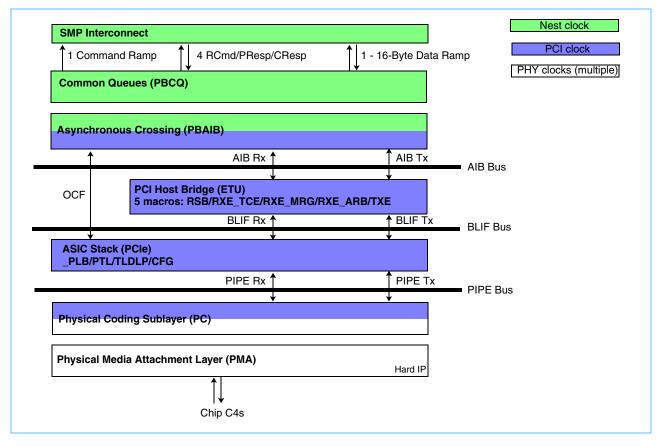

|                                                     | POWER9 PCIe High-Level Diagram<br>Outbound Second-Level Diagram<br>Inbound Second-Level Diagram<br>Atomic Posted Write Address Field<br>Atomic Posted Write Metadata<br>Atomic with Fetch Response Address<br>Atomic Response Data (4-Byte Data)<br>Atomic Response Data (8-Byte Data)<br>CAPI NMMU Request Address Format (Checkout Request) |

# **Revision Log**

Each release of this document supersedes all previously released versions. The revision log lists all significant changes made to the document since its initial release. In the rest of the document, change bars in the margin indicate that the adjacent text was modified fom the previous release of this document.

| Revision Date | Description                                                                                                                                                                                                           |

|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 27 July 2018  | <ul> <li>Version 1.1.</li> <li>Revised a paragraph in Section 5 Processor Bus Common Queue Registers on page 45.</li> <li>Added Table 6-2 PHB Lane Configuration and Swap Bit Register Mapping on page 88.</li> </ul> |

| 31 May 2018   | Version 1.0 (Initial release).                                                                                                                                                                                        |

# About this Document

This document describes the design and operation of the IBM® POWER9<sup>™</sup> <u>PCI</u> Express Controller (PEC). It provides details on its basic requirements, function, operation, and usage. It serves as a reference document for designers, simulators, testers, and programmers.

## **Related Documents**

The documents available in the <u>IBM Portal for OpenPOWER</u>, an online IBM technical library, are helpful in understanding the contents of this document.

## **Conventions Used in this Document**

The following typographical conventions are used to define special terms and command syntax:

| Convention                                                                          | Description                                                                                                                                                                                                                                            |

|-------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Monospaced typeface                                                                 | Used for code examples.                                                                                                                                                                                                                                |

| Number conventions                                                                  | Numbers are generally shown in decimal format, unless designated as follows:<br>• Hexadecimal values are preceded by an "0x". For example: 0x0A00.<br>• Binary values ar preceded by an "0b" (for example: 0b0A00) or enclosed in single quotes ('0'). |

| Underline                                                                           | Indicates that the definition of an acronym is displayed when the user hovers the cursor over the term.                                                                                                                                                |

| <u>Hyperlink</u>                                                                    | Web-based <u>URL</u> s are displayed in blue text to denote a virtual link to an external document. For example: <u>http://www.ibm.com</u>                                                                                                             |

| Note: This is note text.                                                            | The note block denotes information that emphasizes a concept or provides critical information.                                                                                                                                                         |

| This is an inline footnote reference. <sup>1</sup><br>1. Descriptive footnote text. | A footnote is an explanatory note or reference inserted at the foot of the page or under a table that explains or expands upon a point within the text or indicates the source of a citation or peripheral information.                                |

## 1. Overview

The POWER9 PCIe controller (PEC) provides PCIe Gen4 root-complex ports to connect to an adapter slot or as a link to a PCIe switch. It acts as a PCIe host bridge (PHB) from the internal, coherent SMP interconnect to the PCIe I/O.

## 1.1 Description

The PEC is made up of six major building blocks.

- Processor bus common queue (PBCQ) logic

- Processor bus to AIB interface (PBAIB), which is an asynchronous boundary crossing

- Express transaction unit (ETU)

- PCIe <u>ASIC</u> building blocks (PCIASIC)

- Physical coding sublayer (PCS)

- Physical media access (PMA)

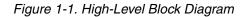

*Figure 1-1* shows an overview of the major blocks and defined interfaces. The following sections describe the building blocks.

#### 1.1.1 Processors Bus Common Queue (PBCQ)