| _ |  |

|---|--|

| - |  |

|   |  |

|   |  |

|   |  |

# PPE 42 & PPE 42X Embedded Processor Core

# **User's Manual**

Version 4.0

September 19, 2019

IBM Corporation Systems Group 11400 Burnet Road Austin, Texas 78758 c/o Michael Floyd, <u>mfloyd@us.ibm.com</u>

Don't Panic

© Copyright International Business Machines Corporation 2019

Printed in the United States of America September 19, 2019

IBM, the IBM logo, and ibm.com are trademarks or registered trademarks of International Business Machines Corp., registered in many jurisdictions worldwide. Other product and service names might be trademarks of IBM or other companies. A current list of IBM trademarks is available on the Web at "Copyright and trademark information" at <u>www.ibm.com/legal/copytrade.shtml</u>.

Other company, product, and service names may be trademarks or service marks of others.

All information contained in this document is subject to change without notice. The products described in this document are NOT intended for use in applications such as implantation, life support, or other hazardous uses where malfunction could result in death, bodily injury, or catastrophic property damage. The information contained in this document does not affect or change IBM product specifications or warranties. Nothing in this document shall operate as an express or implied license or indemnity under the intellectual property rights of IBM or third parties. All information contained in this document was obtained in specific environments, and is presented as an illustration. The results obtained in other operating environments may vary.

**Note:** This document contains information on products in the design, sampling and/or initial production phases of development. This information is subject to change without notice. Verify with your IBM field applications engineer that you have the latest version of this document before finalizing a design. While the information contained herein is believed to be accurate, such information is preliminary, and should not be relied upon for accuracy or completeness, and no representations or warranties of accuracy or completeness are made.

THE INFORMATION CONTAINED IN THIS DOCUMENT IS PROVIDED ON AN "AS IS" BASIS. In no event will IBM be liable for damages arising directly or indirectly from any use of the information contained in this document.

IBM Systems and Technology Group 2070 Route 52, Bldg. 330 Hopewell Junction, NY 12533-6351

The IBM home page can be found at **ibm.com**®.

Version 4.0 September 19, 2019

### Acknowledgments

This manual borrows heavily in organization, substance and style from two other public documents bearing IBM Copyrights:

- PowerPC 405-S Embedded Processor Core, User's Manual, Version 1.2, June 16, 2010. Available from: <u>https://www-01.ibm.com/chips/techlib.nsf/products/PowerPC 405 Embedded Cores</u>

- Power ISA<sup>™</sup>, Version 2.07, May 3, 2013. Available from <u>http://www.power.org</u>

We would like to acknowledge the sizable contributions made to the PPE Architecture and to this document by Bishop Brock (https://github.com/bcbrock) while at IBM.

We also acknowledge the unattributed authors of the above for their contributions to this document.

# **Table of Contents**

| 1 Overview                                             | 12 |

|--------------------------------------------------------|----|

| 1.1 Audience                                           | 13 |

| 1.2 Notation.                                          |    |

| 2 Programming Model                                    | 16 |

| 2.1 Registers                                          |    |

| 2.1.1 Programmer Visible Registers                     |    |

| 2.1.2 Externally Visible Registers.                    |    |

| 2.2 Interface Signals                                  |    |

| 2.3 Privilege Levels                                   |    |

| 2.4 Memory Organization and Addressing                 |    |

| 2.4.1 Data Types and Byte Ordering                     |    |

| 2.4.2 Alignment                                        |    |

| 2.5 Instruction Processing                             |    |

| 2.6 Exception Processing                               |    |

| 2.7 Branch Processing.                                 |    |

| 2.7.1 Branch Target Addressing Options                 |    |

| 2.7.2 Conditional Branch Operations                    | 22 |

| 2.7.3 Fused Compare-Branch Operations                  | 22 |

| 2.8 Precise and Imprecise Memory Accesses              | 23 |

| 2.9 Synchronization                                    |    |

| 2.9.1 Synchronization and Storage Ordering             |    |

| 2.9.2 Synchronization, Interrupts and Error Reporting  |    |

| 2.10 Non-Maskable Interrupts                           |    |

| 2.11 Special-Purpose Registers                         |    |

| 2.11.1 Link Register – LR.                             |    |

| 2.11.2 Count Register – CTR                            |    |

| 2.11.3 Condition Register – CR.                        | 26 |

| 2.11.3.1 CR[CR0] Fields After Comparison Instructions  | 27 |

| 2.11.3.2 CR[CR0] Fields After Update-Form Instructions |    |

| 2.11.3.3 mtcr0 and mfcr                                |    |

| 2.11.4 Fixed-Point Exception Register – XER.           |    |

| 2.11.5 Machine State Register – MSR.                   |    |

| 2.11.5.1 Interrupt Processing and Control              |    |

| 2.11.5.2 WAIT mode<br>2.11.5.3 Imprecise Mode Enable   |    |

| 2.11.5.4 SIB Error Reporting and Accumulation.         |    |

| 2.11.5.5 Low-Priority Mode                             |    |

| 2.11.5.6 Instance-Specific Control                     |    |

| 3 Initialization, Reset, and Starting Execution        |    |

| •                                                      |    |

| 3.1 Initial State                                      |    |

| 3.2 Reset Operations.                                  |    |

| 3.3 Core State Subsequent to a Reset Event.            |    |

| 3.4 Starting Instructions.                             |    |

| 3.5 System Reset Interrupt Handler                     |    |

| 4 Interrupts and Exceptions                            |    |

| 4.1 Architectural Definitions and PPE 42 Behavior      |    |

| 4.1.1 Interrupt Precision                              | 35 |

| 4.1.2 Asynchronous, Synchronous, and Machine Check Interrupts               | 36   |

|-----------------------------------------------------------------------------|------|

| 4.1.2 Asynchronous, cynchronous, and Machine Oneck menupis                  |      |

| 4.2 Interrupt Vector Offsets                                                |      |

|                                                                             |      |

| 4.3 Interrupt Handling.                                                     |      |

| 4.3.1 Interrupt Masking                                                     |      |

| 4.3.2 Interrupt Priority                                                    |      |

| 4.3.3 Interrupt Processing                                                  | .40  |

| 4.3.4 Interrupt Halt Semantics                                              |      |

| 4.3.5 Unmaskable Interrupt Promotion                                        |      |

| 4.4 General Interrupt Handling Registers                                    |      |

| 4.4.1 Machine State Register – MSR                                          |      |

| 4.4.2 Save/Restore Registers 0 and 1 – SRR0/1                               |      |

| 4.4.3 Interrupt Vector Prefix Register – IVPR                               |      |

| 4.4.4 Interrupt Status Register – ISR                                       |      |

| 4.4.5 Error Data Register – EDR                                             |      |

| 4.5 Detailed Interrupt Descriptions                                         | 43   |

| 4.5.1 Machine Check Interrupt – PPE 42 Vector x'000'; PPE 42X Vector x'020' |      |

| 4.5.1.1 Service Interface Bus (SIB) Error Reporting and Handling            | 44   |

| 4.5.1.2 Instruction Machine Check Handling                                  | 45   |

| 4.5.1.3 Data Machine Check Handling for Load-Type Operations                | 46   |

| 4.5.1.4 Data Machine Check Handling for Store-type Operations               |      |

| 4.5.1.5 Machine Checks Promoted from Other Unmaskable Interrupts            |      |

| 4.5.2 System Reset Interrupt – Vector x'040'                                |      |

| 4.5.3 Data Storage Interrupt – Vector x'060'                                |      |

| 4.5.4 Instruction Storage Interrupt – Vector x'080'                         |      |

| 4.5.5 External Interrupt – Vector x'0A0'                                    |      |

| 4.5.5.1 External Interrupt Recognition; Phantom Interrupt Avoidance         | .52  |

| 4.5.6 Alignment Interrupt – Vector x'0C0'                                   |      |

| 4.5.7 Program Interrupt – Vector x'0E0'                                     |      |

| 4.5.8 Decrementer (DEC) Interrupt – Vector x'100'                           |      |

| 4.5.9 Fixed Interval Timer (FIT) Interrupt – Vector x'120'                  |      |

| 4.5.10 Watchdog Timer (WDT) Interrupt – Vector x'140'                       |      |

| 5 Timer Facilities                                                          |      |

|                                                                             |      |

| 5.1 The Decrementer (DEC)                                                   |      |

| 5.1.1 Using DEC as a Programmable Interval Timer                            | 59   |

| 5.1.2 Using DEC to Emulate a Timebase                                       |      |

| 5.2 The Fixed Interval Timer (FIT)                                          |      |

| 5.3 The Watchdog Timer (WDT)                                                |      |

| 5.3.1 Implications of TSR[ENW]                                              | . 62 |

| 5.4 Debug Behavior                                                          |      |

| 5.5 Reset Behavior                                                          | . 62 |

| 6 External Interface Registers                                              | .63  |

| 5                                                                           |      |

| 7 Debugging                                                                 |      |

| 7.1 External Debug Mode                                                     |      |

| 7.2 Processor Control                                                       |      |

| 7.3 Processor Status                                                        |      |

| 7.3.1 Status outputs                                                        |      |

| 7.3.1.1 Halted indication                                                   |      |

| 7.3.1.2 Watchdog Timeout indication                                         |      |

| 7.3.1.3 Error indications                                                   | . 67 |

| 7.4 Debug Registers                                                         |      |

| 7.4.1 DACR – Debug Address Compare Register                                 | . 69 |

| 7.4.2 DBCR – Debug Control Register                                           |     |

|-------------------------------------------------------------------------------|-----|

| 7.4.3 EDR – Error Data Register                                               |     |

| 7.4.4 ISR – Interrupt Status Register                                         |     |

| 7.4.5 XCR – External Control Register<br>7.4.6 XSR – External Status Register |     |

| 7.5 Debug Events                                                              |     |

| 7.5.1 Trap Events                                                             |     |

| 7.5.2 Instruction-Address Comparison Events                                   | 70  |

| 7.5.3 Data-Address Comparison Events                                          |     |

| 7.5.4 Zero Address Comparison.                                                |     |

| 7.5.5 Data Address Comparison and Alignment                                   | 72  |

| 7.6 Halt Processing                                                           |     |

| 7.6.1 Definition of Halted                                                    |     |

| 7.6.2 Entering the Halted state                                               |     |

| 7.6.3 Halt Conditions and Error indication                                    | 73  |

| 7.6.4 Exiting the Halted state                                                |     |

| 7.6.5 Halting and Synchronization                                             |     |

| 7.7 Single-Stepping and Ramming                                               |     |

| 7.7.1 Single-Stepping                                                         | 74  |

| 7.7.1.1 Single-stepping and Exceptions                                        |     |

| 7.7.2 Ramming                                                                 |     |

| 7.8 Debugging Procedures                                                      |     |

| 7.8.1 Basic Debugging Procedures                                              |     |

| 7.8.1.1 Halting the Processor.                                                |     |

| 7.8.1.2 Force-Halting the Processor.                                          |     |

| 7.8.1.3 Clearing Debug Halt Status.                                           |     |

| 7.8.1.4 Resetting the Processor.                                              |     |

| 7.8.1.5 Restarting the Processor.                                             |     |

| 7.8.1.6 Single-Stepping an Instruction<br>7.8.1.7 Ramming an Instruction      | /0  |

|                                                                               |     |

| 7.8.1.8 Low-overhead Ramming<br>7.8.1.9 Toggling XSR[TRH]                     |     |

| 7.8.2 Advanced Debugging Procedures                                           |     |

| 7.8.2.1 Reading Status and IAR Contents Simultaneously                        |     |

| 7.8.2.2 Reading Status and SPRG0 Simultaneously                               |     |

| 7.8.2.3 Writing IR and SPRG0 Simultaneously                                   |     |

| 7.8.2.4 Writing XCR and SPRG0 Simultaneously                                  |     |

| 7.8.2.5 Writing XSR and IAR Simultaneously.                                   |     |

| 7.8.2.6 Reading CTR                                                           |     |

| 7.8.2.7 Reading SRR0 and LR Simultaneously                                    |     |

| 7.8.2.8 Reading GPR pairs (VDRs) Simultaneously                               |     |

| 8 Register Summary                                                            | .81 |

| 8.1 Reserved Registers                                                        |     |

| 8.2 Reserved Fields                                                           |     |

| 8.3 General Purpose Registers                                                 |     |

| 8.4 Virtual Doubleword Registers                                              |     |

| 8.5 Machine State Register and Condition Register.                            |     |

| 8.6 Special Purpose Registers                                                 |     |

| 8.6.1 Using SPRs as Scratch Registers                                         |     |

| 8.7 External Interface Registers                                              |     |

| 8.8 Simultaneous Update                                                       |     |

| 8.9 Initialization and Reset                                                  |     |

| 8.10 Alphabetical Listing of PPE 42 Registers                                 | 86  |

|                                                                               |     |

| 8.10.1 CR – Condition Register                  |     |

|-------------------------------------------------|-----|

| 8.10.2 CTR – Count Register                     |     |

| 8.10.3 DACR – Debug Address Compare Register    |     |

| 8.10.4 DBCR – Debug Control Register            |     |

| 8.10.5 DEC – Decrementer                        |     |

| 8.10.6 EDR – Error Data Register                | 93  |

| 8.10.7 IAR – Instruction Address Register       | 94  |

| 8.10.8 IR – Instruction Register                | 95  |

| 8.10.9 ISR – Interrupt Status Register          | 96  |

| 8.10.10 IVPR – Interrupt Vector Prefix Register | 98  |

| 8.10.11 LR – Link Register                      | 99  |

| 8.10.12 MSR – Machine State Register            | 100 |

| 8.10.13 PIR – Processor Identification Register |     |

| 8.10.14 PVR – Processor Version Register        |     |

| 8.10.15 SPRG0 – SPR General 0                   |     |

| 8.10.16 SRR0 – Save Restore Register 0          |     |

| 8.10.17 SRR1 – Save Restore Register 1          |     |

| 8.10.18 TCR – Timer Control Register.           |     |

| 8.10.19 TSR – Timer Status Register.            |     |

| 8.10.20 XCR – External Control Register         |     |

| 8.10.21 XER – Fixed Point Exception Register    |     |

| 8.10.22 XSR – External Status Register          | 113 |

| 9 Instruction Set                               |     |

|                                                 |     |

| 9.1 Instruction Set Origin and Portability      |     |

| 9.2 Rationale for the PPE 42 Instruction Set    |     |

| 9.2.1 PPE 42X Added Instructions                |     |

| 9.2.2 PPE 42 New Instructions                   |     |

| 9.2.3 PPE 42X New Instructions                  |     |

| 9.3 Instruction Formats                         |     |

| 9.3.1 PPE 42 Specific Instruction Format        |     |

| 9.3.2 PPE 42X Specific Instruction Format       |     |

| 9.4 Alphabetical Instruction Listing            | 122 |

| 9.4.1 add                                       | 123 |

| 9.4.2 addc                                      | 124 |

| 9.4.3 adde                                      | 125 |

| 9.4.4 addi                                      | 126 |

| 9.4.5 addic                                     | 127 |

| 9.4.6 addic                                     | 128 |

| 9.4.7 addis                                     | 129 |

| 9.4.8 addme                                     | 130 |

| 9.4.9 addze                                     | 131 |

| 9.4.10 and                                      | 132 |

| 9.4.11 andc                                     |     |

| 9.4.12 andi                                     |     |

| 9.4.13 andis                                    |     |

| 9.4.14 b                                        |     |

| 9.4.15 bc                                       |     |

| 9.4.16 bcctr                                    |     |

| 9.4.17 bclr.                                    |     |

| 9.4.18 bnbw                                     |     |

| 9.4.19 bnbwi                                    |     |

| 9.4.20 clrbwbc                                  |     |

| 9.4.21 clrbwibc                                 |     |

|                                                 | 0   |

| 9.4.22 cmplw   | 151 |

|----------------|-----|

| 9.4.23 cmplwbc | 152 |

| 9.4.24 cmplwi  |     |

| 9.4.25 cmpw    |     |

| 9.4.26 cmpwbc  |     |

| 9.4.27 cmpwi   |     |

| 9.4.28 cmpwibc |     |

| 9.4.29 cntlzw. |     |

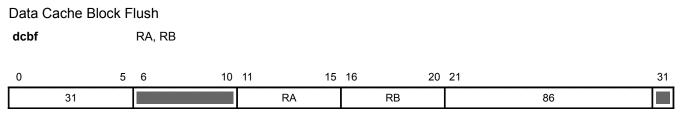

| 9.4.30 dcbf    |     |

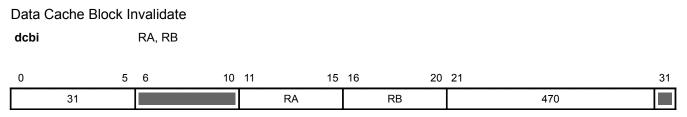

| 9.4.31 dcbi    |     |

| 9.4.32 dcbg    |     |

| 9.4.33 dcbt    |     |

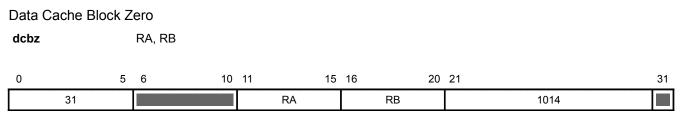

| 9.4.34 dcbz    |     |

| 9.4.35 eqv     |     |

| 9.4.36 extsb   |     |

| 9.4.30 extsb   |     |

| 9.4.37 exisit  |     |

|                |     |

| 9.4.39 lbzu    |     |

| 9.4.40 lbzx    |     |

| 9.4.41 lcxu    |     |

| 9.4.42 lhz     |     |

| 9.4.43 lhzu    |     |

| 9.4.44 lhzx    |     |

| 9.4.45 lsku    |     |

| 9.4.46 lvd     | 186 |

| 9.4.47 lvdu    |     |

| 9.4.48 lvdx    |     |

| 9.4.49 lwz     | 189 |

| 9.4.50 lwzu    | 190 |

| 9.4.51 lwzx    | 191 |

| 9.4.52 mfcr    | 192 |

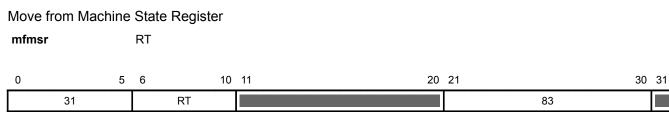

| 9.4.53 mfmsr   | 193 |

| 9.4.54 mfspr   |     |

| 9.4.55 mtcr0   |     |

| 9.4.56 mtmsr   |     |

| 9.4.57 mtspr   |     |

| 9.4.58 mullhw  |     |

| 9.4.59 mulhwu  |     |

| 9.4.60 mulli   |     |

| 9.4.61 mulw    |     |

| 9.4.62 nand    |     |

| 9.4.63 neg     |     |

| 0              |     |

| 9.4.64 nor     |     |

| 9.4.65 or      |     |

| 9.4.66 orc     |     |

| 9.4.67 ori     |     |

| 9.4.68 oris    |     |

| 9.4.69 rfi     |     |

| 9.4.70 rldicl  |     |

| 9.4.71 rldicr  |     |

| 9.4.72 rldimi  | 213 |

| 9.4.73 rlwimi  | 214 |

| 9.4.74 rlwinm  | 215 |

| 9.4.75 rlwnm   | 217 |

|                |     |

| 9.4.76 slvd                        | 218   |

|------------------------------------|-------|

| 9.4.77 slw                         | . 219 |

| 9.4.78 sraw                        | . 220 |

| 9.4.79 srawi                       | . 221 |

| 9.4.80 srvd                        | . 222 |

| 9.4.81 srw                         | . 223 |

| 9.4.82 stb                         | . 224 |

| 9.4.83 stbu                        | . 225 |

| 9.4.84 stbx                        | . 226 |

| 9.4.85 stcxu                       | . 227 |

| 9.4.86 sth                         | . 230 |

| 9.4.87 sthu                        | 231   |

| 9.4.88 sthx                        | . 232 |

| 9.4.89 stsku                       | . 233 |

| 9.4.90 stvd                        | . 236 |

| 9.4.91 stvdu                       | 237   |

| 9.4.92 stvdx                       | . 238 |

| 9.4.93 stw                         | . 239 |

| 9.4.94 stwu                        | . 240 |

| 9.4.95 stwx                        | . 241 |

| 9.4.96 subf                        | 242   |

| 9.4.97 subfc                       | 243   |

| 9.4.98 subfe                       | . 244 |

| 9.4.99 subfic                      | . 245 |

| 9.4.100 subfme                     | 246   |

| 9.4.101 subfze                     | . 247 |

| 9.4.102 sync                       | . 248 |

| 9.4.103 tw                         | . 249 |

| 9.4.104 wrtee                      | . 251 |

| 9.4.105 wrteei                     | . 253 |

| 9.4.106 xor                        | . 255 |

| 9.4.107 xori                       | . 256 |

| 9.4.108 xoris                      | . 257 |

| 9.5 Instruction Set Mnemonics List | 258   |

|                                    |       |

### Source Documents

The latest version of this document can be accessed internal to IBM via the following URL:

https://ibm.box.com/ Link for PPE 42X Core Users Manual.pdf

The source documents for this document can be accessed internal to IBM via the following URL:

https://ibm.box.com/ Link for PPE42X Users Manual folder

Note that change bars for sub-documents of Open Office master documents are treated inconsistently by Open Office in general, and may be lost when Open Office master documents are rendered into PDF. In order to view change markings of sub-documents it may be necessary to view the Open Office sub-documents directly.

### **Revision History**

| Version | Date       | Changes                         |        |

|---------|------------|---------------------------------|--------|

| 4.0     | 09/16/2019 | First "official" PPE42X Release | mfloyd |

### Cross Reference Table

The following table is included as a reference for future editing. Cross-references between sub-documents must be inserted and named explicitly. Note that when viewing a sub-document that references another sub-document, these cross references will appear as "Error: Reference not found" even when they are valid references. It will be necessary to view a printed or PDF version of the document to check whether cross-sub-document references are correct.

#### Table 1: Sub-document Cross Reference Table

| PPE 42 Core Overview                  |                                           |  |  |  |

|---------------------------------------|-------------------------------------------|--|--|--|

| Тад                                   | Reference                                 |  |  |  |

| PPE                                   | PPE 42 Core Programming Model             |  |  |  |

| Тад                                   | Reference                                 |  |  |  |

| precise and imprecise memory accesses | 1.8 Precise and Imprecise Memory Accesses |  |  |  |

| MSR                                   | 1.12.5 Machine State Register - MSR       |  |  |  |

| wait mode                             | 1.12.5.2 WAIT mode                        |  |  |  |

| PPE 4                                 | 2 Core Initialization and Reset           |  |  |  |

| Тад                                   | Reference                                 |  |  |  |

| initialization and reset              | 1 Initialization and Reset                |  |  |  |

| PPE 42                                | Core Interrupts and Exceptions            |  |  |  |

| Тад                                   | Reference                                 |  |  |  |

| interrupts and exceptions             | 1 Interrupts and Exceptions               |  |  |  |

| interrupt vector offsets              | 1.2 Interrupt Vector Offsets              |  |  |  |

| general interrupt handling registers  | 1.6 General Interrupt Handling Registers  |  |  |  |

| PF                                    | PE 42 Core Timer Facilities               |  |  |  |

| Тад                                   | Reference                                 |  |  |  |

| timer facilities                      | 1 Timer Facilities                        |  |  |  |

| PPE 42 0                              | Core External Interface Registers         |  |  |  |

| Тад                                   | Reference                                 |  |  |  |

| external interface registers          | 1 External Interface Registers            |  |  |  |

|                                       | PPE 42 Core Debugging                     |  |  |  |

| Тад                                   | Reference                                 |  |  |  |

| debugging                             | 1 Debugging                               |  |  |  |

| PI                                    | PE 42 Core Instruction Set                |  |  |  |

| Тад                                   | Reference                                 |  |  |  |

| PPE                                   | E 42 Core Register Summary                |  |  |  |

| Тад                                   | Reference                                 |  |  |  |

| register summary                      | 1 Register Summary                        |  |  |  |

| virtual doubleword registers          | 1.4 Virtual Doubleword Registers          |  |  |  |

| special purpose registers             | 1.6 Special Purpose Registers             |  |  |  |

## 1 Overview

Il semble que la perfection soit atteinte non quand il n'y a plus rien à ajouter, mais quand il n'y a plus rien à retrancher.

It seems that perfection is attained not when there is nothing left to add, but when there is nothing left to take away.

- Antoine de Saint-Exupéry

The Power ISA Lite Processing Engine (PPE, pronounced "peppy") model 42 embedded processor core implements an extended subset of the Power ISA<sup>™</sup> Version 2.07 specification. PPE 42 is a 32-bit processor, with extensions that provide for atomic loads and stores of 64-bit data. PPE 42 implements subsets or modified subsets of the Power ISA 32-bit User Instruction Set Architecture, Virtual Environment Architecture and Embedded Operating Environment Architecture. PPE 42X is fully based on the PPE 42 processor and additionally implements a modified subset of the Power ISA 64-bit User Instruction Set Architecture. PPE 42 and PPE 42X also implement several instructions and capabilities unique to each processor.

As an extended subset of the Power ISA, PPE 42 is *not* Power ISA compliant, and the architectural features specific to PPE will *not* be included in future Power ISA specifications. PPE 42 is derived from the Power ISA to take advantage of the synergies of design, verification, tools and firmware development within the IBM POWER Systems development organization that would not be realized if any other architecture for PPE 42 had been chosen. The PPE architecture supports the PowerPC Embedded Application Binary Interface (EABI) for 32-bit processors, which is critical to allow the modification of existing PowerPC compiler infrastructures with minimum effort. PPE 42X adds native support for managing the stack frame compatible with EABI Version 4.

The PPE architecture balances area-efficiency with function and performance. PPE 42 implements only 16 of the 32 Power ISA general purpose registers (GPRs) along with a selected set of special-purpose registers (SPRs), comprising less than 1000 bits of architected state. A large subset of the 97 implemented instructions can execute pipelined in a single cycle; other instructions execute in two or three cycles plus any memory or synchronization delays. PPE 42X implements an additional 9 instructions as an extension of the PPE 42 Instruction Set, consisting of 7 single cycle arithmetics and 2 new multi-cycle load and store instructions to assist with stack frame and processor context management.

This user's manual provides an architectural overview, programming model, and detailed functional information about the PPE 42 and 42X embedded processor cores. The information in this user's manual includes details on the instruction set, registers, and the various functions and functional units of the core including interrupts, timers and debugging infrastructure.

This manual only covers the PPE 42 and 42X processor core itself. The PPE 42 core provides interfaces that allow it to be integrated with a variety of memory and peripheral subsystems. Therefore many aspects of a complete embedded processing system architecture are not covered in this manual, and will be documented with the specific instantiations of the core. These aspects include caches, memory management, peripheral units and system-level error handling.

## **1.1 Audience**

This book is for system hardware and software engineers who are engaged in hardware development, firmware and operating system support, and application software development. This manual assumes an understanding of embedded processor design, embedded system design, operating systems and reduced instruction set computing (RISC). The reader may also find it useful to refer to the Power ISA Version 2.07 specification, available from www.power.org.

## 1.2 Notation

The table below describes the notational conventions used in this manual.

### Table 1.1: Notational Conventions

| Notation                        | tion Meaning                                                                                                                                                                                                                                               |  |

|---------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| n                               | A decimal number                                                                                                                                                                                                                                           |  |

| x'n n'                          | A hexadecimal number                                                                                                                                                                                                                                       |  |

| 'n n'                           | A binary number                                                                                                                                                                                                                                            |  |

| =                               | Assignment                                                                                                                                                                                                                                                 |  |

| ٨                               | AND logical operator                                                                                                                                                                                                                                       |  |

| 7                               | NOT logical operator                                                                                                                                                                                                                                       |  |

| V                               | OR logical operator                                                                                                                                                                                                                                        |  |

| $\oplus$                        | Exclusive-OR (XOR) operator                                                                                                                                                                                                                                |  |

| +                               | Twos complement addition                                                                                                                                                                                                                                   |  |

| -                               | Twos complement subtraction, unary minus                                                                                                                                                                                                                   |  |

| ×                               | Multiplication                                                                                                                                                                                                                                             |  |

| ÷                               | Division yielding a quotient                                                                                                                                                                                                                               |  |

| %                               | Remainder of an integer division                                                                                                                                                                                                                           |  |

|                                 | Concatenation                                                                                                                                                                                                                                              |  |

| =, ≠                            | Equal, not equal relations                                                                                                                                                                                                                                 |  |

| <, >                            | Signed comparison results                                                                                                                                                                                                                                  |  |

| < <sup>u</sup> , > <sup>u</sup> | Unsigned comparison results                                                                                                                                                                                                                                |  |

| If then else                    | Conditional execution; if <i>condition</i> then <i>a</i> else <i>b</i> , where <i>a</i> and <i>b</i> represent one or more pseudocode statements. Indenting indicates the ranges of <i>a</i> and <i>b</i> . If <i>b</i> is null, the else does not appear. |  |

| do                              | Do loop. "to" and "by" clauses specify incrementing an iteration variable; "while"<br>and "until" clauses specify terminating conditions. Indenting indicates the scope<br>of a loop.                                                                      |  |

| leave                           | Leave innermost do loop or do loop specified in a leave statement.                                                                                                                                                                                         |  |

| FLD                             | An instruction or register field                                                                                                                                                                                                                           |  |

| FLDb                            | A bit in a named instruction or register field                                                                                                                                                                                                             |  |

| FLD <sub>b:b</sub>              | A range of bits in a named instruction or register field                                                                                                                                                                                                   |  |

| REG <sub>b</sub>                | A bit in a named register                                                                                                                                                                                                                                  |  |

| REG <sub>b:b</sub>              | A range of bits in a named register                                                                                                                                                                                                                        |  |

| REG[FLD]                        | A field in a named register                                                                                                                                                                                                                                |  |

| REG[FLD, FLD]                   | ] A list of fields in a named register                                                                                                                                                                                                                     |  |

| (Rx)                            | The contents of a GPR specified as an instruction field, where x is A, B, S or T                                                                                                                                                                           |  |

| (RA 0)                          | The contents of the register RA, or 0 if RA is 0                                                                                                                                                                                                           |  |

| n <sub>b</sub>                  | The bit or bit value b replicated n times                                                                                                                                                                                                                  |  |

| EXTS(x)                         | The result of extending x on the left with sign bits (high-order bits)                                                                                                                                                                                     |  |

| CIA                             | Current instruction address; The 32-bit address of the instruction being described by a sequence of pseudocode.                                                                                                                                            |  |

| NIA                             | Next instruction address; The 32-bit address of the next instruction to be executed. In pseudocode, a successful                                                                                                                                           |  |

### PPE 42 Embedded Processor Core

| Notation      | Meaning                                                                                                                                                               |  |  |

|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|               | branch is indicated by assigning a value to NIA. For instructions that do not branch, the NIA is CIA +4.                                                              |  |  |

| MS(addr, n)   | The <i>n</i> bytes at the location in main storage represented by <i>addr</i> .                                                                                       |  |  |

| EA            | Effective address; the 32-bit address, derived by applying indexing or indirect addressing rules to the specified operand, that specifies a location in main storage. |  |  |

| ROTL((RS), n) | Rotate left; the contents of RS are rotated left the number of bits specified by n                                                                                    |  |  |

| MASK(MB, ME)  | Mask having ones in positions MB through ME (wrapping if MB > ME) and zeros elsewhere.                                                                                |  |  |

| DW(xy)        | A series of Virtual Doubleword Registers or pairs of concatenated Special Purpose Registers, numbered x to y                                                          |  |  |

| DW(n)         | Doubleword register n, selected from a series of registers                                                                                                            |  |  |

| GPR(r)        | General Purpose Register r, where $0 \le r \le 31$                                                                                                                    |  |  |

| VDR(r)        | Virtual Doubleword Register r, where $0 \le r \le 31$                                                                                                                 |  |  |

| (GPR(r))      | The contents of GPR(r)                                                                                                                                                |  |  |

| (VDR(r))      | The contents of VDR(r)                                                                                                                                                |  |  |

| (DW(n))       | The contents of DW(n)                                                                                                                                                 |  |  |

| (LR)          | The contents of the Link Register.                                                                                                                                    |  |  |

# 2 Programming Model

This sections covers aspects of the PPE 42 programming model that are not discussed elsewhere in this manual.

## 2.1 Registers

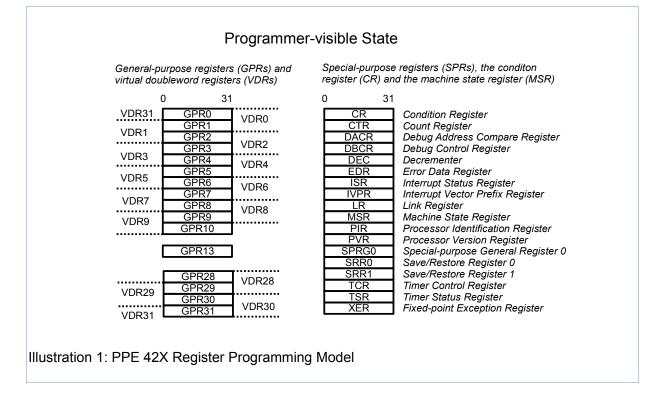

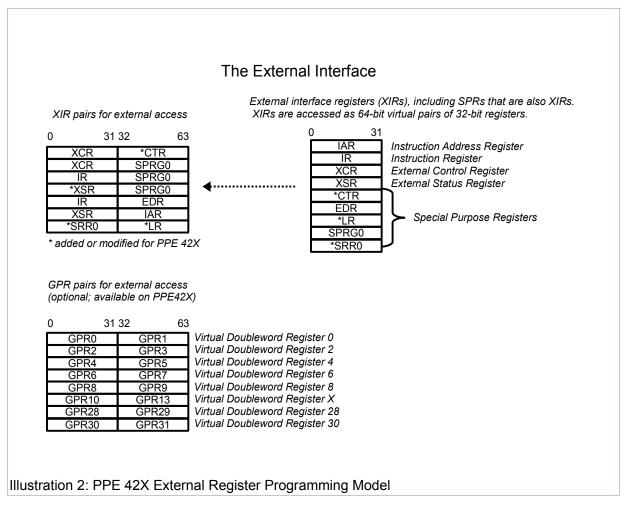

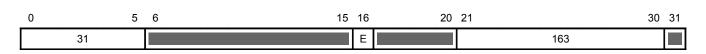

The following two illustrations show the PPE 42X register programming model from either a programmer or an external user's view.

### 2.1.1 Programmer Visible Registers

The programmer-visible state, which is the same for both PPE 42 and PPE42X, includes sixteen 32-bit general-purpose registers (GPRs), and eighteen 32-bit special-purpose registers (SPRs). Pairs of consecutively-numbered (modulo 32) GPRs can be used as virtual doubleword registers (VDRs) for 64-bit loads and stores, in addition to selected 64-bit shift and rotate arithmetics in the PPE 42X.

### 2.1.2 Externally Visible Registers

External control and status is provided by 4 dedicated 32-bit external interface registers (XIRs). Two SPRs (EDR and SPGR0) on PPE 42 are both SPRs and XIRs, with three additional XIR-accessible SPRs (CTR, LR, and SRR0) on PPE 42X. Although architected as 32 bit registers, XIRs are always accessed as 64-bit pairs of 32-bit registers. PPE 42X provides optional access to the even-numbered VDRs (0,2,4,6,8,28, & 30), as well as a psuedo "VDRX" consisting of the GPR10\_GPR13 pair, such that all 16 GPRs are readily visible when this feature is enabled.

## 2.2 Interface Signals

The table below details the major input and output signals of the PPE 42 core that bear on the programming model. The table is not intended as a complete hardware specification, but is only included to help clarify which operations are fully internal to the core vs. those operations controlled by and dependent on the instance-specific environment.

Table 1.2: Selected PPE 42 Core I/O Signals

| Dir. | Signal        | Bits | Notes                                                                                              |

|------|---------------|------|----------------------------------------------------------------------------------------------------|

| out  | inst_req_addr | 32   | A 32-bit, 4-byte aligned instruction address is presented to the memory interface, which returns a |

| Dir. | Signal            | Bits | Notes                                                                                                                                                                                                                       |  |

|------|-------------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| in   | instruction       | 32   | 4-byte instruction.                                                                                                                                                                                                         |  |

| out  | data_req_addr     | 32   | 32-bit data addresses are presented to the memory interface.<br>The PPE 42 core supports 8, 16, 32, and 64-bit atomic loads and stores.                                                                                     |  |

| in   | load_data         | 64   |                                                                                                                                                                                                                             |  |

| out  | store_data        | 64   |                                                                                                                                                                                                                             |  |

| in   | halt_req          | 1    | Instance-specific logic external to the core can force the core to halt by asserting this signal.                                                                                                                           |  |

| in   | hreset_req        | 1    | Instance-specific logic external to the core can force the core to reset by asserting this signal.                                                                                                                          |  |

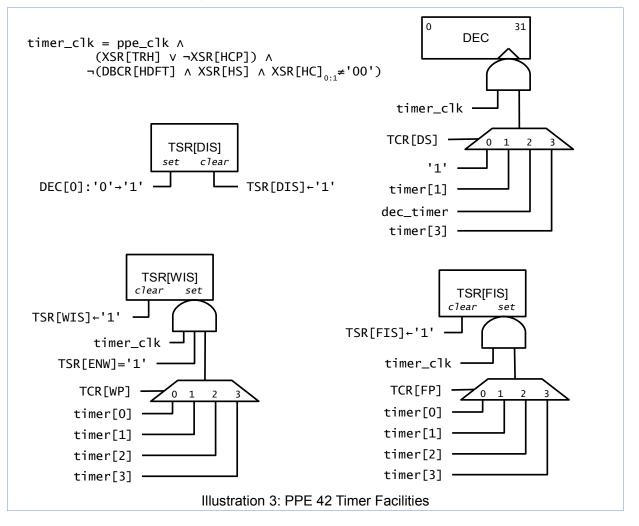

| in   | timer             | 4    | These four events can be programmably selected as the Fixed Interval Timer and Watchdog Timer events.                                                                                                                       |  |

| in   | dec_timer         | 1    | This event can be programmably selected as the decrementer event.                                                                                                                                                           |  |

| in   | ext_intr          | 1    | Indication from instance-specific logic external to the core that causes an External Interrupt exception event.                                                                                                             |  |

| out  | arb_high_priority | 1    | Allows PPE code with time sensitive requirements to choose to run with heightened priority memory accesses, if supported by the instance-specific environment.                                                              |  |

| out  | error             | 1    | Pulses to indicate that the PPE is now halted due to an error condition occurring.<br>May be used by instance-specific logic external to the core to record status or take an action in response to this event.             |  |

| out  | watchdog_timeout  | 1    | Pulses to indicating that a watchdog timeout occurred and caused the PPE to either halt or result May be used by instance-specific logic external to the core to record status or take an action in response to this event. |  |

| out  | halted            | 1    | Signal indicating that the core is in a halted state (for any reason).<br>May be used by instance-specific logic external to the core to record status or take an action in<br>response to this event.                      |  |

## 2.3 Privilege Levels

The PPE 42 architecture does not support privilege levels. All processor resources are available to all programs at all times. For this reason the Power ISA **sc** (system call) instruction is neither required nor implemented by PPE 42. It is up to the programming, external hardware and/or operating environments to enforce code and data separation disciplines if required.

## 2.4 Memory Organization and Addressing

The PPE 42 architecture defines a 32-bit, 4 GB flat address space for instructions and data memory. Almost every feature of the memory subsystem is instance specific however and will be documented with each instance of the PPE 42 core. Instance specific features not defined by this manual include memory maps of defined memory regions, cacheability, access restrictions, speculation, prefetching and addressability and alignment requirements.

Regarding addressability, PPE 42 supports a byte-addressable memory subsystem. Byte addressability is not required however, and the PPE 42 architecture specifically allows accesses to word- and/or doubleword addressable memory spaces to appear as though they were unaligned byte-addressable accesses. The memory subsystem may also signal exceptions for disallowed or ambiguous accesses, for example in response to a byte store to a word-addressable control register space. Again, the interpretation of any memory address is fully instance specific.

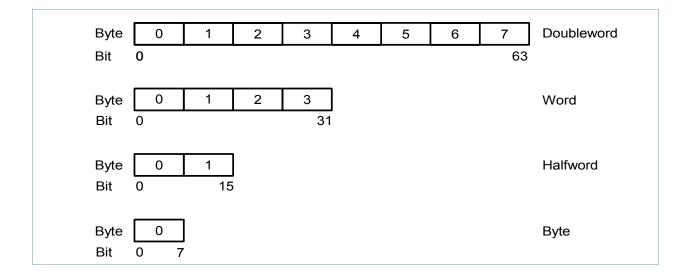

### 2.4.1 Data Types and Byte Ordering

The data types consist of bytes (8 bits), halfwords (2 bytes), words (4 bytes) and doublewords (8 bytes). The figure below illustrates the data types, and also shows their bit and byte definitions for big-endian representation of values. Note that PPE 42 bit numbering is reversed from industry conventions; bit 0

represents the most significant bit of a value. PPE 42 does not support little-endian byte ordering.

PPE 42 only supports the doubleword data type for loads and stores targeting *virtual doubleword* registers. The concept of a virtual doubleword is described in section 8.4, *Virtual Doubleword Registers*. PPE 42 does not implement 64-bit arithmetic or logical instructions, however PPE 42X supports doubleword data types for its five 64-bit shift and rotate instructions.

### 2.4.2 Alignment

PPE 42 instruction addresses are always presented to the memory interface 4-byte aligned. It is architecturally impossible for the PPE 42 core to request an unaligned instruction address.

Alignment requirements for loads and stores are instance specific and will be documented with each instance. The PPE 42 core presents effective memory addresses to the memory interface as specified with each instruction description, and all alignment exceptions originate from the memory interface, never from the PPE 42 core proper. The only architectural requirement for alignment exceptions is that for the **dcbz** instruction, the memory interface is required to generate an alignment exception if the access is to a non-cacheable memory area, and the memory interface itself does not emulate the **dcbz** instruction.

The data cache control instructions **dcbf**, **dcbi**, **dcbt** and **dcbz** are required to ignore any low-order bits of the effective address that specify bytes within a cache block, and to treat the address of any byte within a cache block as referring to the cache block as a whole. PPE 42 does not specify a cache block size, other than the requirement that the cache block size be an even power of two, greater than or equal to eight.

## 2.5 Instruction Processing

The PPE 42 core executes instructions in sequential program order. The core supports pipelining of arithmetic, logical and compare instructions only, as these instructions are guaranteed to complete without exception or stalling once they have been successfully decoded. All other instructions are fully fetched, decoded and executed before the next instruction is fetched. Instructions are never fetched speculatively, and the PPE 42 core does not implement branch prediction.

The PPE 42 core executes instructions in two or three cycles, plus memory and synchronization delays. Instructions are fetched and decoded in a single cycle, then most instructions are executed the following cycle assuming no memory delays. Fused compare-branch and synchronizing instructions require a third

cycle. As mentioned previously, execution of arithmetic, logical and compare instructions can be overlapped with the fetch and decode of the following instruction, effectively supporting single-cycle execution for a large class of instructions.

The PPE 42 core supports memory subsystems that provide either single-cycle or delayed responses to instruction fetches and data requests. Although the PPE 42 core implements the *Harvard Architecture*, with separate interfaces for instruction and data accesses, the instruction and data interfaces are never active on the same cycle, thus load, store and cache management instructions require a minimum of two cycles to complete.

The following table details the instruction classes as recognized by the core microarchitecture along with their instruction timings. The table assumes single-cycle instruction access, so does not include any latency in the memory subsystem.

| Instruction Instruction(s) Issue Rate |                                                                         | Issue Rate (Cycles)                                                                                 | Notes                                                                                                                                                                                                                                                                                                                                                                                |  |  |

|---------------------------------------|-------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| <b>A</b><br>Arithmetic                | Arithmetic,<br>logical, compare,<br><b>mfspr, mfcr,</b><br><b>mtcr0</b> | 1                                                                                                   | Since these instructions always complete without exception the cycle after being fetched and decoded, PPE 42 provides single-cycle pipelined execution of Class A instructions.                                                                                                                                                                                                      |  |  |

| <b>D</b><br>Data                      | Load, store, <b>dcb</b> *                                               | 2 + memory delay                                                                                    | These instructions potentially require blocking while waiting for a response from the memory interface.                                                                                                                                                                                                                                                                              |  |  |

| <b>B</b><br>Branch                    | b, bc, bcctr, bclr                                                      | 2                                                                                                   | All branches are fully resolved prior to fetching the next instruction.                                                                                                                                                                                                                                                                                                              |  |  |

| <b>F</b><br>Fused                     | Fused compare-<br>branch                                                | 3                                                                                                   | The fused compare-branch instructions execute serialized in 3 cycles.<br>Fused compare-branch instructions provide a code-space advantage but<br>not a direct performance advantage over executing the two underlying<br>instructions.                                                                                                                                               |  |  |

| <b>K</b><br>Load or Store<br>Stack    | lsku, stsku                                                             | Load = (4 to 24) + (1 to<br>11) memory delays).<br>Store = (6 to 26) + (3<br>to 13) memory delays). | an EABI-compliant stack frame then provide an atomic update of the stack pointer. These instructions potentially require blocking while waiting for                                                                                                                                                                                                                                  |  |  |

| M mtspr, wrtee, 2<br>Move to wrteei   |                                                                         | 2                                                                                                   | All <b>mtspr</b> , <b>wrtee</b> and <b>wrteei</b> execute serialized in 2 cycles. Since many SPRs control asynchronous exceptions, this allows the core to provide a sequential execution model in the presence of asynchronous exceptions. Note that neither the Power ISA nor typical programming applications require <b>wrtee</b> and <b>wrteei</b> to be context synchronizing. |  |  |

| <b>C</b><br>Context<br>synchronizing  | mfmsr, mtmsr,<br>rfi                                                    | 3 + context<br>synchronization                                                                      | <b>mfmsr, mtmsr</b> and <b>rfi</b> are implemented as context synchronizing instructions by the PPE 42 core. Execution is suspended until all preceding instructions have reported any exceptions they might report.                                                                                                                                                                 |  |  |

| <b>S</b><br>Storage<br>synchronizing  | sync                                                                    | 3 + storage<br>synchronization                                                                      | <b>sync</b> stalls for storage synchronization, which extends context synchronization in certain cases.                                                                                                                                                                                                                                                                              |  |  |

| <b>T</b><br>Trap Word                 | tw                                                                      | 1                                                                                                   | trap form is never executed, but instead always causes an exception or halt.<br>mark form is executed as a no-op and causes a trace marker for debug.                                                                                                                                                                                                                                |  |  |

Table 1.3: PPE 42 Core Instruction Classes and Timing

## 2.6 Exception Processing

Exceptions are processed in two machine cycles, plus any delays associated with execution synchronization of the memory interface.

Asynchronous exceptions are implemented as occurring between instructions, specifically before the execution of the next instruction. Synchronous exceptions are implemented as occurring during the execution of an instruction, but before any of the effects of the instruction have been committed to the GPR

state. For further information see section 4, *Interrupts and Exceptions*.

PPE 42 Embedded Processor Core

### 2.7 Branch Processing

The PPE 42 core does not implement branch prediction or any other type of speculative instruction fetching. Whenever a conditional branch instruction is encountered, the next instruction access request to the memory subsystem will always be the correct instruction with respect to the branch condition.

### 2.7.1 Branch Target Addressing Options

The unconditional branch instruction (**b**) carries the displacement to the branch target address as a signed 26-bit value (the 24-bit LI field right-extended with '00'). The displacement enables unconditional branches to cover an address range of  $\pm$ 32 MB.

The conditional branch instruction (**bc**) carries the displacement to the branch target address as a signed 16-bit value (the 14-bit BD field right-extended with '00'). The displacement enables conditional branches to cover an address range of  $\pm 32$  KB.

The PPE 42 fused compare-branch instructions (**bnbw**, **bnbwi**, **clrbwbc**, **clrbwibc**, **cmplwbc**, **cmpwbc**, and **cmpwibc**) carry the displacement to the branch target address as a signed 12-bit value (the 10-bit BDX field right-extended with '00'). The displacement enables fused compare-branches to cover an address range of ±2 KB.

For the relative forms of **b** and **bc** (AA is set to '0'), and for all fused compare-branch instructions, the target address is the address of the branch instruction (CIA) plus the signed displacement.

For the absolute (AA is set to '1') forms of **b** and **bc**, the target address is '0' plus the signed displacement. If the sign bit (LI[0] or BD[0]) is '0', the displacement is the target address. If the sign bit is '1', the displacement is a negative value and wraps to the highest memory addresses. For example, if the displacement of an unconditional branch is x'3FFF FFC' (the 26-bit representation of -4), the target address is x'FFFF FFFC' (0 - 4 bytes, or 4 bytes below the top of memory).

### 2.7.2 Conditional Branch Operations

Conditional branch instructions can test a CR[CR0] bit. The value of the BI field specifies the bit to be tested. The BO field controls whether the CR bit is tested.

The BO field of the conditional branch instruction specifies the conditions used to control branching, and specifies how the branch affects the CTR. Conditional branch instructions can decrement the CTR by one, and after the decrement, test the CTR value.

For details see the descriptions of the **bc**, **bclr** and **bcctr** instructions.

### 2.7.3 Fused Compare-Branch Operations

PPE 42 fused compare-branch instructions update CR[CR0] either as the result of a comparison (**cmplwbc**, **cmpwbc**, **cmpwibc**) or as the result of a 32-bit value computation (**bnbw**, **bnbw**, **clrbwbc**, **clrbwibc**).

For the comparison forms, the branch is taken if a bit of the resulting CR[CR0] specified by the BIX field has the same value as the PIX field of the instruction. For the value forms, the branch is controlled by the PIX field and the EQ bit (bit 2) of CR[CR0].

For details see the descriptions of the individual fused compare-branch instructions.

Version 4.0

### 2.8 Precise and Imprecise Memory Accesses

The PPE 42 core implements a hazard-free pipeline. Load-use dependencies are eliminated by requiring all loads to complete in the GPRs before the instruction following the load is executed. This means that the PPE 42 pipeline always stalls for loads, and all errors caused by load instructions are reported precisely.

PPE 42 provides an option to allow the memory subsystem to treat stores imprecisely. Imprecise mode allows the memory interface to process store requests in parallel with continued instruction processing by the core. This may increase performance, at the expense of precise error reporting and recovery.

The imprecise option is selected by setting MSR[IPE] to '1'. Whether the memory subsystem of a PPE 42 instance supports imprecise mode for any interface is instance specific, however if an instance does support imprecise mode then imprecise stores are only allowed when MSR[IPE] = '1'.

The number of outstanding store requests, and the ordering of store completion with respect to a single memory or multiple memories in imprecise mode is instance-specific. Since PPE 42 is an in-order core, it can be guaranteed however that stores are always presented to the memory interface in program order. In precise mode, all errors for loads, stores and all cache management operations are presented precisely. This means that in the event of an error causing an interrupt, SRR0 will contain the address of the erroneous load, store or cache management instruction.

In imprecise mode, errors from stores and all cache management operations may be presented imprecisely. This means that in the event of an error causing a machine check interrupt, SRR0 may not contain the address of the erroneous instruction, but instead may contain the address of a subsequent instruction. However, the EDR will contain the data address associated with the imprecise operation that reported the error. It is also possible that multiple imprecise errors may be reported simultaneously in imprecise mode, and in this case it is instance-specific which of the erroneous memory addresses is reported in the EDR.

Note that even though loads are always precise, an imprecise error for a previous imprecise store or cache management instruction may be reported by a load instruction. In fact, imprecise errors may be reported on *any* type of instruction if the instruction is interrupted by an asynchronous interrupt, and imprecise errors are pending in the memory subsystem. Careful analysis of the EDR, ISR, SRR0 and SRR1 may be required to diagnose and recover from errors in imprecise mode.

The processor always begins execution of interrupt handlers in precise mode. Imprecise mode is enabled and disabled by using the **mtmsr** instruction to modify MSR[IPE]. Since both of these events are context synchronizing, all imprecise errors caused by instructions previous to the entry of the interrupt handler, or previous to the execution of the **mtmsr** instruction will have been reported before execution can continue. Therefore it is never possible for the program to receive a new imprecise error if MSR[IPE] = '0'.

## 2.9 Synchronization

The following types of synchronization are recognized:

- **Execution Synchronization**: This type of synchronization guarantees that all instructions preceding the synchronizing instruction have completed in the previous context, including the reporting of any and all exceptions the preceding instructions may report.

- **Context Synchronization**: Context synchronization extends execution synchronization with the further requirement that all instructions subsequent to the synchronizing instruction execute in the context established by the synchronizing instruction.

- **Storage Synchronization**: This type of synchronization extends execution synchronization with the further requirement that all storage accesses by the preceding instructions have completed with respect to all mechanisms that access storage.

- Sequential Execution with Respect to Asynchronous Interrupts: This type of synchronization guarantees that if any instruction causes or unmasks an asynchronous exception, the associated asynchronous interrupt will be taken before the next sequential instruction is executed.

The PPE 42 core guarantees sequential execution with respect to asynchronous interrupts by serializing any instruction that might cause or unmask an asynchronous interrupt, then taking such an interrupt (or another higher priority interrupt if also pending) prior to fetching the next sequential instruction. The instructions implemented this way are all **mtspr**, **wrtee** and **wrteei**.

PPE 42 implements all synchronizing instructions as context synchronizing. This fact plus sequential execution with respect to asynchronous interrupts means that in general, PPE 42 programs would not require the Power ISA **isync** instruction, therefore PPE 42 does not implement **isync**. The PPE 42 context synchronizing instructions are **mfmsr**, **mtmsr**, **rfi** and **sync**. The **sync** instruction is also storage synchronizing.

### 2.9.1 Synchronization and Storage Ordering

The PPE 42 core never executes loads out of order, therefore loads are always completed in program order, and any instruction following a load is never executed until the load completes.

Handling of stores is instance-specific. To guarantee store ordering and completion, two methods are available:

- 1. A series of one or more stores can be followed by a **sync** instruction, to guarantee that all preceding stores are complete before proceeding.

- 2. The processor can be placed into precise mode (MSR[IPR] = '0') prior to a sequence of stores.

As discussed earlier, in precise mode stores are required to complete up to the point of exception reporting before the core is allowed to continue. For most anticipated memory interfaces, this type of completion is equivalent to storage synchronization. Exceptions would include memory units like write-gathering bus bridges that might report error-free transaction completion immediately, but not flush local buffer contents to the final destination memory (and signal memory synchronization) until later.

### 2.9.2 Synchronization, Interrupts and Error Reporting

All interrupts are context synchronizing. Whenever an unmasked exception is present, the interrupt taken will always be the highest priority interrupt after execution synchronization. The MSR after execution synchronization is saved in SRR1, and execution continues at the interrupt vector in the context of the new MSR as defined for each interrupt. The MSR saved in SRR1 will record Service Interface Bus (SIB) status of all instructions preceding the interrupt. Similarly, since **mfmsr** is context synchronizing, the value returned by the **mfmsr** instruction includes the SIB status of all instructions preceding the **mfmsr** instruction. See further below for a discussion of the SIB abstraction.

When an interrupt handler returns by executing an **rfi**, if a synchronous imprecise exception is pending in the memory interface it will be reported as an interrupt in lieu of executing the **rfi**. This means that SRR0 and SRR1 will be destroyed, and the **rfi** instruction will not be directly recoverable in this case.

### 2.10 Non-Maskable Interrupts

The machine check, program, data storage, instruction storage and alignment interrupts are considered *non-maskable*. These interrupts are required to either be processed as soon as they occur, or immediately halt the processor.

The machine check interrupt is taken as an interrupt only if MSR[ME] is '1'. The other unmaskable interrupts are taken as specified only if MSR[UIE] = '1'. However, if a non-maskable interrupt (other than a machine check) occurs when MSR[UIE] = '0' but MSR[ME] = '1', the interrupt is *promoted* and taken as a machine check interrupt. When an interrupt is promoted, all of the ISR updates of the original interrupt take place, however execution continues at the machine check interrupt vector and ISR[MCS] is set to indicate that the machine check interrupt was due to a promoted unmaskable interrupt.

If an unmaskable interrupt can not be taken as an interrupt due to MSR[ME] = '0', then the core processes the interrupt up to the point that the first instruction of the interrupt vector would be fetched, and then halts. Halts due to unmaskable interrupts are reported in the XSR as XSR[HC] = '011'.Service Interface Bus (SIB)

The PPE 42 core provides special architectural resources and error reporting for transactions on a *Service Interface Bus* (SIB). It is instance-specific whether an instance of PPE 42 provides a SIB abstraction, and how it is mapped into the flat 4 GB address space if present.

The SIB abstraction is a memory interface that provides up to 8 unique return codes for memory transactions, where return code 0 indicates "success". The remaining 7 return codes are not otherwise interpreted by the PPE 42 core, however for data transactions these 7 codes can be individually enabled and disabled from causing a machine check exception. Instruction execution from SIB memory spaces is also supported, however non-0 return codes for SIB instruction accesses are always considered fatal errors and cause a machine check exception.

If a SIB access returns a 0 return code, the assumption is that data loaded into GPRs is correct, and data stored to SIB memories has been stored correctly. In the event of non-0 SIB return codes, the data loaded into a GPR, and the effect on the environment for stores is instance specific.

SIB error control and reporting fields appear in the machine state register (MSR). For further details on SIB support please see the following section 2.11.5, Machine State Register – MSR.

## 2.11 Special-Purpose Registers

All PPE 42 registers and their fields are documented in section 8, *Register Summary*. This section covers Special-Purpose Registers (SPRs) that are integral to the PPE 42 programming model but not otherwise described in detail in this manual.

### 2.11.1 Link Register – LR

The LR is written from a GPR using the **mtspr** (**mtlr**) instruction, and read into a GPR using the **mfspr** (**mflr**) instruction. LR is also updated by branch instructions that have the LK bit set to 1. These branch instructions load the LR with the address of the next instruction that follows the branch instruction. Thus, the LR contents can be used as the return address for a subroutine that was called using the branch.

The LR contents can be used as a target address for the branch conditional to link register (**bclr**) instruction. This allows branching to any address.

When the LR contents are used as an instruction address,  $LR_{30:31}$  are ignored and substituted with '00' on the instruction interface, as all instruction addressess must be word-aligned. However, when the LR is read or written using an **mfspr** or **mtspr** instruction, all 32 bits are read or written.

With careful programming the LR can also be used as a 32-bit scratch register.

### 2.11.2 Count Register – CTR

The CTR is written from a GPR using the **mtspr** (**mtctr**) instruction, and read into a GPR using the **mfspr** (**mfctr**) instruction.