# OpenPOWER I/O Design Architecture

# Version 2

Workgroup Specification

Revision 1.0.0 (February 17, 2016)

penPOWER

www.openpowerfoundation.org

### **OpenPOWER I/O Design Architecture: Version 2**

Revision 1.0.0 (2016-02-17) Copyright © 2016 OpenPOWER Foundation

All capitalized terms in the following text have the meanings assigned to them in the OpenPOWER Intellectual Property Rights Policy (the "OpenPOWER IPR Policy"). The full Policy may be found at the OpenPOWER website or are available upon request.

This document and translations of it may be copied and furnished to others, and derivative works that comment on or otherwise explain it or assist in its implementation may be prepared, copied, published, and distributed, in whole or in part, without restriction of any kind, provided that the above copyright notice and this section are included on all such copies and derivative works. However, this document itself may not be modified in any way, including by removing the copyright notice or references to OpenPOWER, except as needed for the purpose of developing any document or deliverable produced by an OpenPOWER Work Group (in which case the rules applicable to copyrights, as set forth in the OpenPOWER IPR Policy, must be followed) or as required to translate it into languages other than English.

The limited permissions granted above are perpetual and will not be revoked by OpenPOWER or its successors or assigns.

This document and the information contained herein is provided on an "AS IS" basis AND TO THE MAXIMUM EXTENT PERMIT-TED BY APPLICABLE LAW, THE OPENPOWER Foundation AS WELL AS THE AUTHORS AND DEVELOPERS OF THIS STAN-DARDS FINAL DELIVERABLE OR OTHER DOCUMENT HEREBY DISCLAIM ALL OTHER WARRANTIES AND CONDITIONS, EITHER EXPRESS, IMPLIED OR STATUTORY, INCLUDING BUT NOT LIMITED TO, ANY IMPLIED WARRANTIES, DUTIES OR CONDITIONS OF MERCHANTABILITY, OF FITNESS FOR A PARTICULAR PURPOSE, OF ACCURACY OR COMPLETENESS OF RESPONSES, OF RESULTS, OF WORKMANLIKE EFFORT, OF LACK OF VIRUSES, OF LACK OF NEGLIGENCE OR NON-INFRINGEMENT.

OpenPOWER, the OpenPOWER logo, and openpowerfoundation.org are trademarks or registered trademarks of OpenPOWER Foundation, Inc., registered in many jurisdictions worldwide. Other company, product, and service names may be trademarks or service marks of others.

This document is the workproduct of the OpenPOWER Foundation Hardware Architecture Workgroup. Acknowledgement to members of the workgroup for their contributions

## **Table of Contents**

| Preface                                                | vi  |

|--------------------------------------------------------|-----|

| 1. Conventions                                         |     |

| 2. Document change history                             | vi  |

| 1. About This Document                                 | 1   |

| 1.1. Purpose                                           | . 1 |

| 1.2. Numbering Conventions                             |     |

| 1.3. Reference Documentation                           |     |

| 1.4. OpenPOWER Foundation Standards Track Work Product | . 1 |

| 2. Introduction                                        | 2   |

| 2.1. Conformance to this Specification                 |     |

| 2.2. General Information                               |     |

| 3. Design Specifics                                    | 6   |

| 3.1. High-Level Specifics                              |     |

| 3.2. Lower-Level Details                               |     |

| A. Endpoint Partitioning                               |     |

| A.1. Endpoint Partitioning Overview                    | 49  |

| A.2. Endpoint Partitioning Functional Specifics        | 50  |

| B. No-Translate Operation                              |     |

| B.1. No-Translate Example                              |     |

| C. Glossary                                            | 60  |

| D. OpenPOWER Foundation overview                       |     |

| D.1. Foundation documentation                          |     |

| D.2. Technical resources                               | 63  |

| D.3. Contact the foundation                            | 64  |

# **List of Figures**

| 3.1. PE# Determination for DMA and Error Messages                                       | . 9 |

|-----------------------------------------------------------------------------------------|-----|

| 3.2. PCIe Non-MSI DMA Operation Address Fields                                          | 15  |

| 3.3. DMA Operation High-Level Diagram - No Page Migration                               | 16  |

| 3.4. I/O Address Validation and TCE Translation Implementation for 32-Bit DMA Addresses | 19  |

| 3.5. I/O Address Validation and TCE Translation Implementation for 64-Bit DMA Addresses | 21  |

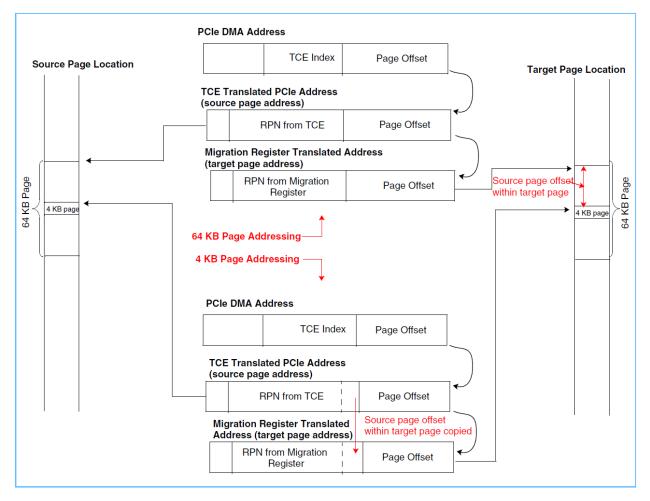

| 3.6. Memory Migration Operation for a 64 KB Page and a 4 KB Page within the 64 KB Page  | 27  |

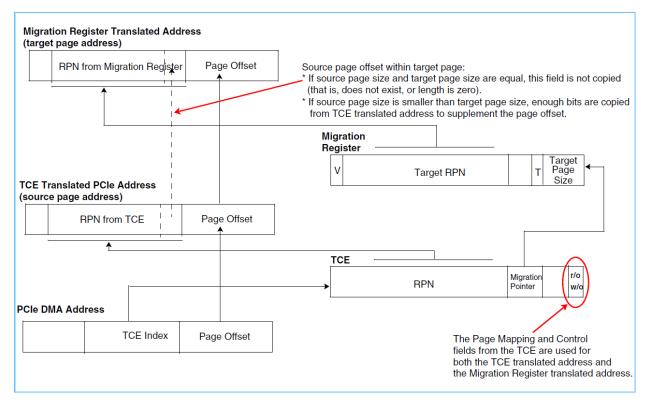

| 3.7. Source and Destination Page Address Creation for DMA to a Page Being Migrated      | 28  |

| 3.8. PCIe Normal DMA Operation for a Three-Level TCE Table                              | 31  |

| 3.9. MSI Flow                                                                           | 37  |

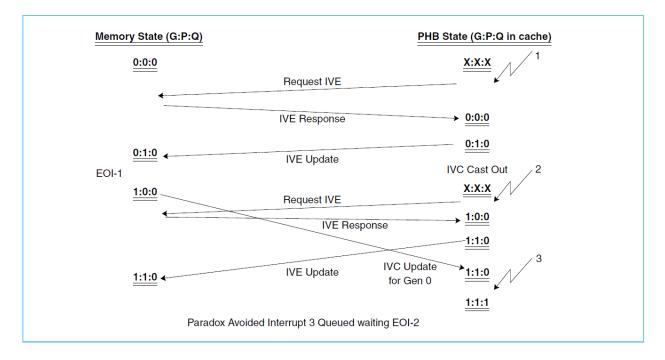

| 3.10. Example Interrupt State Bit Flow                                                  | 39  |

| 3.11. Example EOI Update Race                                                           | 40  |

| 3.12. Example EOI Update Race Controlled with Generation Number Field                   | 40  |

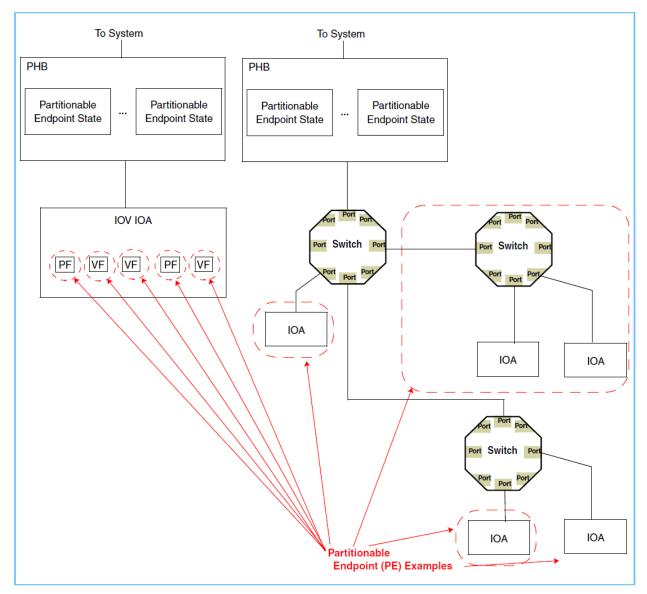

| A.1. Example System Configurations: Partitionable Endpoint (PE) Definition              | 50  |

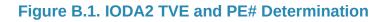

| B.1. IODA2 TVE and PE# Determination                                                    | 58  |

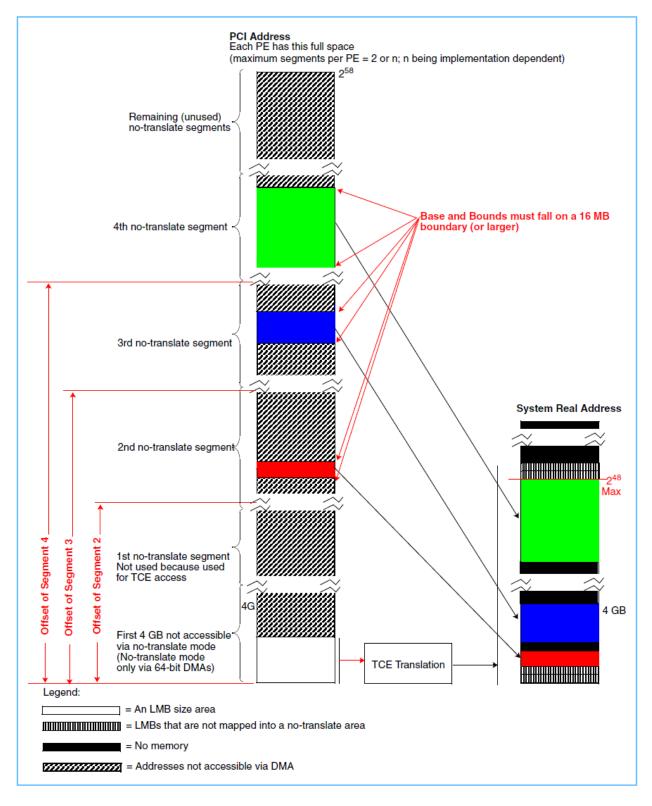

| B.2. Example Physical Address Map with TCE Bypass Enabled for Some PEs                  | 59  |

## **List of Tables**

| 0  |

|----|

| 0  |

| 0  |

| 4  |

| 23 |

| 24 |

| 25 |

| 0  |

| 32 |

| 3  |

| 4  |

| 8  |

| 2  |

| 2  |

| 3  |

| 4  |

| 4  |

| -6 |

| 7  |

| 57 |

|    |

# Preface

## **1.** Conventions

The OpenPOWER Foundation documentation uses several typesetting conventions.

### **Notices**

Notices take these forms:

#### Note

A handy tip or reminder.

#### Important

Something you must be aware of before proceeding.

#### Warning

Critical information about the risk of data loss or security issues.

## **Command prompts**

- **\$ prompt** Any user, including the root user, can run commands that are prefixed with the \$ prompt.

- # **prompt** The root user must run commands that are prefixed with the # prompt. You can also prefix these commands with the **sudo** command, if available, to run them.

## **2. Document change history**

This version of the guide replaces and obsoletes all earlier versions.

The following table describes the most recent changes:

| Revision Date    | Summary of Changes                                                                                                                                                    |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| January 13, 2016 | <ul> <li>Revision 1.0.0 - Workgroup Specification</li> <li>Clean-up markings and rev #.</li> <li>Clean-up legal wording and added foundation info appendix</li> </ul> |

| October 1, 2015  | <ul> <li>Revision 09 Public Review Draft</li> <li>Clean-up of typo/conversion errors.</li> </ul>                                                                      |

| August 21, 2015  | Revision 09 Public Review Draft                                                                                                                                       |

| April 23, 2015   | <ul> <li>Creation based on IBM IODA2 Specification - revision 1.0</li> <li>Updates from Hardware Architecture WG review of original submission</li> </ul>             |

# **1. About This Document**

# **1.1. Purpose**

The purpose of the I/O Design Architecture, version 2 (IODA2) specification is to describe the chip architecture for key aspects of PCIe® based host bridge (PHB) designs for IBM® POWER8<sup>™</sup> systems.

## **1.2. Numbering Conventions**

Big-endian numbering of bytes and bits is used in this document unless otherwise indicated. In bigendian systems, numbering of bits starts at 0 for the most significant bit and continues to the least significant bit. Little-endian numbering might be implied by the bit-ordering sequence in figures or text where the low-numbered bits are on the right. For example, [31:0] is little-endian ordering and [0:31] is big-endian ordering.

## **1.3. Reference Documentation**

For additional information, see IBM Power Architecture® Platform Requirements (PAPR).

## **1.4. OpenPOWER Foundation Standards Track** Work Product

This document is an OpenPOWER Foundation Standards Track Work Product, and is intended to progress through these steps:

- 1. Work Group Specification Draft

- 2. Work Group Specification Public Review Draft

- 3. Work Group Specification

- 4. Candidate OpenPOWER Standard

- 5. OpenPOWER Standard

- 6. Approved Errata

# **2. Introduction**

The purpose of the I/O Design Architecture, version 2 (IODA2) specification is to describe the chip architecture for key aspects of PCIe®-based host bridge (PHB) designs for IBM® POWER8<sup>™</sup> systems.

The following terminology is used in this document:

- The term "real" used in relationship to addresses means "processor real address."

- The term "PCI" is used to describe the most recent versions of all forms of PCI® standards. Where there are significant differences between individual PCI standards, the following terminology is used to differentiate between the PCI® standards: conventional PCI®, PCI-X®, and PCI-Express®. For example, POWER8 implements PCIe Gen 3.

- The term "MSI" is used to refer to "MSI" and "MSI-X", generically. Where there are differences, the distinction is made in context.

- The term "implementation dependent" is used to refer to specifics beyond the scope of this architecture, which should be provided in the implementation's specification.

For the definitions of more terms and acronyms used in this document, see the Appendix C, Glossary [60].

## **2.1. Conformance to this Specification**

Any implementation of this specification must adhere to the following set of numbered conformance clauses to claim conformance to this specification (or any optional portion of it):

- 1. Hardware Requirement: The PCI host bridge (PHB) hardware must implement all the requirements specified as "Hardware Requirements" in this architecture, unless otherwise required by the specific requirement.

- 2. Firmware Requirement: The platform firmware must implement all the requirements specified as "Firmware Requirements" in this architecture, unless otherwise required by the specific requirement.

## **2.2. General Information**

This section provides some general background on translation control entries (TCEs), message signalled interrupts (MSIs), enhanced I/O error handling (EEH), and direct memory access (DMA) ordering rules.

## 2.2.1. I/O Load/Store Address Space

*Load* and *Store* instructions that are issued to addresses that target I/O adapter (IOA) memory or I/O address ranges <sup>1</sup> are called memory mapped I/O (MMIO).

<sup>&</sup>lt;sup>1</sup>There are three PCI address ranges: configuration, I/O, and memory. The I/O space is primarily for legacy material; its use is discouraged by PCI-X and later versions of the architecture in favor of the memory address space. This document primarily addresses the memory address space, as used by both MMIO and DMA. Some reference are made to the I/O space as it relates to MMIO.

### 2.2.2. TCEs

Translation control entries (TCEs) are to I/O what page table entries (PTEs) are to the processor. That is, they translate from one address space to another. In particular, TCEs translate from an I/O bus memory address to a physical system memory address. The TCEs perform the following functions:

- Expand the I/O address space addressing for IOAs that cannot access all of the system memory address space. For example, a 32-bit IOA must have its address expanded for systems with more than 4 GB of system memory. Otherwise, such an IOA has to DMA its data to and from a buffer in the lower address range. The processor has to move the data from and to the real target page in memory.

- Provide indirection in addressing:

- —For logical partitioning (LPAR), it is necessary to hide the real address of the memory from the partitions.

- —For dynamic logical partitioning (DLPAR) and memory migration, and for virtual partition memory, it is necessary to be able to move the physical memory transparently under the IOA from one location to another.

- —For virtual I/O, the address of the memory in the client partition must be hidden from the server partition.

- —Assist some IOAs by providing hardware scatter-gather. This provides the IOA with a contiguous address space instead of one that is broken at every 4K page boundary. This can actually improve the performance of some IOAs if the platform can perform the TCE manipulation faster than the IOA can process scatter/gather lists.

- Provide extra protection from IOA hardware, microcode, and device driver bugs by providing readonly and write-only (as well as read-write) protection through two control bits in the TCE.

### 2.2.3. MSIs

The PCI architecture allows signalling of interrupts in either of two ways:

- Through a signal pin.<sup>2</sup> This is called a level-signalled interrupt, or LSI.

- Through a message. This is called a message-signalled interrupt, or MSI.<sup>3</sup>

MSIs have the advantage of pushing an IOA's DMA data that it has previously written ahead of it. Therefore, when the interrupt is presented, the device driver (DD) knows that the data is in the processor's coherency domain. That is, it is immediately available.

There is no such guarantee with an LSI. Therefore, when the DD sees an LSI, it must perform a *Load* instruction targeted to its IOA. Then, it must wait for the *Load* data to return before being assured that the previously DMAed data is available to be used. This *Load* is a performance penalty. In addition, PCIe allows only four LSIs per PHB, which severely restricts usability.

<sup>&</sup>lt;sup>2</sup>For PCIe, the LSI interrupts are not signalled by a physical pin (sometimes called out-of-band signalling), but rather through a logical pin that is shipped across the PCIe fabric as a packet (sometimes called in-band signalling).

<sup>&</sup>lt;sup>3</sup>The "message" for MSI is really a DMA write operation to a special address with special data, as far as the IOA and the I/O fabric are concerned.

LSIs are defined by this architecture, but MSI and MSI-X are the focus. PCI defines:

- For base MSI: Up to 32 interrupts per function of the IOA. The IOA can have up to eight functions, giving up to 256 interrupts per IOA.

- For MSI-X: Up to 2K interrupts per function of the IOA. The IOA can have up to eight functions, giving up to 16K interrupts per IOA.

However, this flexibility comes at a cost in the scalability of the interrupt controller structure. This architecture addresses the scalability issue by placing the interrupt vector structures and interrupt state in system memory. It has firmware assist with the interrupt state machine during end of interrupt (EOI) processing and with the processing of missed interrupts while an MSI is disabled.

## 2.2.4. EEH

Enhanced error handling (EEH) is a powerful technology developed by IBM to prevent I/O errors from propagating to the system and causing unrecoverable errors, which generally bring down the operating system. EEH is a required technology for logically partitioned systems, so that an error in the I/O subsystem of one partition does not affect the other LPAR partitions.

EEH stops operations to and from an IOA when an error is detected with that IOA. This stopped condition is called the Stopped state <sup>4</sup>. The Stopped state has the following key requirements:

- The IOA function must be prevented from completing the I/O operation in error so that the requester of the I/O operation does not use bad data.

- The Stopped state must appear to a DD to be isolated to just that DD. This implies extra hardware or firmware to support the continuation of the I/O operation of other IOA functions when an error is generated from another IOA function.

#### Exceptions:

In the following cases, the DDs for these functions must coordinate any Stopped state recovery:

- For a plug-in adapter where the EEH functionality is implemented above the physical plug-in connector and where the plug-in adapter has multiple IOA functions on it under a PCI-to-PCI bridge

- For an IOA that has multiple functions on it, and for which there exist multiple DDs (potentially one per function)

- Software (DD or above) must not be able to introduce an error that can cause a Stopped state of other IOA functions. That is, it must not introduce a stopped-state error to IOA functions other than the ones controlled by the DD.

- —Software might, for example, improperly set up the TCEs for an I/O operation or pass the wrong address to its IOA. This can cause an access to a TCE that is invalid. (The TCE is not set up, or the TCE is set to read-only for a write or to a PCI atomic operation or write-only for a read or PCI atomic operation.) This causes a Stopped state.

- —It is acceptable for a platform hardware error, but not a DD or IOA function hardware error, to affect multiple IOA functions. However, the recovery from such an error must be transparent to the DD. That is, the platform makes it appear to all IOA functions that they have encountered the error condition themselves.

<sup>&</sup>lt;sup>4</sup>Sometimes this state is also referred to as the "freeze" state or condition. In addition, the IOA Stopped state can be broken down into the MMIO Stopped state and the DMA Stopped state. In this document, if "MMIO" or "DMA" is not specified along with "Stopped state", the reference is either to the general concept or to both the MMIO and DMA Stopped states.

- OpenPOWER I/O Design Architecture

- The DD must be able to detect the Stopped state condition.

- The DD (and, therefore, the platform) must be able to remove its IOA function from the MMIO Stopped state for MMIO operations, independent of other IOA functions.

- —The capturing of fault information for problem determination must be allowed after the Stopped state condition occurs.

- The DD (and, therefore, the platform) must be able to remove the IOA function from the DMA Stopped state for DMA operations independent of other IOA functions. The DD is responsible for bringing its IOA function to a known good state before removing it from the DMA Stopped state, to avoid the possibility of improper operations from its IOA function. In many cases, the DD needs to bring its IOA function back to the reset state or as close to the reset state as possible, and then restart any incomplete operations.

- The platform must not pass along MSI interrupts from the IOA function while the IOA function is in the DMA Stopped state.

# **3. Design Specifics**

This chapter describes applicable design specifics as they apply to IBM POWER8<sup>™</sup> systems. The designs in this chapter are not the only designs that meet the Power Architecture Platform Requirements (PAPR). However, to enable design sharing and to prevent firmware impacts from one implementation to the next, the designs in this chapter are more or less "fixed" unless negotiation between the hardware and firmware designers provide changes to this direction. (That is, the changes become a chip I/O architecture.) Anyone making changes to these design points must ensure that the changes allow the designs to continue to meet the architectures specified in the PAPR.

This chapter does not provide the detailed definitions (bits, bytes, and addresses) of the registers needed to implement these designs. However, the stability of those is no less important. Designers of chips that generate the same buses are expected to use the same register definitions whenever possible to reduce the impact to firmware implementations.

Each implementation is expected to devise a consistent way to self-identify its capabilities. For example, a register or set of registers, or some sort of informational header in the chip's register space, can be used. This document does not propose a way to do this.

## **3.1. High-Level Specifics**

Endpoint partitioning is the concept of being able to identify operations to or from an individual partitionable endpoint (PE) across an I/O fabric. For more information, see Appendix A, Endpoint Partitioning [49].

## **R1-3.1-1** Hardware Requirement:

The PCI host bridge (PHB) hardware must implement all the requirements specified as "Hardware Requirements" in this architecture, unless otherwise required by the specific requirement.

## **R1-3.1-2** Firmware Requirement:

The platform firmware must implement all the requirements specified as "Firmware Requirements" in this architecture, unless otherwise required by the specific requirement.

## **3.2. Lower-Level Details**

# **3.2.1. PE# Determination, PE State, EEH, and Error Injec-**tion

The PHB hardware determines, for any given operation, the PE numbers (PE#s) to which the operation belongs. It tracks the state of that PE# so that it can stop the PE on an error and prevent further operations after the error. It does this on a per PE# basis so that nonaffected PEs can continue to operate while the affected PE is recovered. For more information, see Section 3.2.1.3, "PE State and EEH" [12].

The PE# determination is made during the following operations:

- MMIO operations: The address is decoded and a range or multiple ranges of addresses are assigned to each PE#. This is done in an implementation-dependent way. For requirements, see Section 3.2.1.1, "MMIO PE# Determination" [7].

- DMA or MSI operations or error message from the PCIe link: The requester ID (RID) associated with the operation is used as an index into an RID translation table (RTT). For requirements, see Section 3.2.1.2, "DMA and Error Message PE# Determination, RTT, RTC Invalidate, and PELT-V" [7].

- ---If the operation is a DMA or MSI operation, the PE# field of the RID translation entry (RTE) indicates the PE# associated with the RID.

- —If the operation is an error message, the PE# field is the index of the PE lookup table (vector) (PELT-V). When the PELT-V is accessed, the entry indicates, by a vector of bits, which PE#s are affected by the RID. PELT-V entries are generated by firmware for all PE#s. That is, the depth of the PELT-V is equal to the number of PEs implemented. Hierarchical RIDs, such as switch RIDs and IOV PFs, have more than one bit set in the PE look-up entry (vector) (PELE-V). Single RIDs, such as those for VFs, have only one bit set.

#### **3.2.1.1. MMIO PE# Determination**

PHBs are required to support MMIO address-space decoding and the assignment of PE#s to those decodes, as specified by requirements in this section. How this is implemented is implementation dependent.

#### R1-3.2.1.1-1 Hardware Requirement:

The PHB hardware must support the decoding of MMIO addresses, and both of the following conditions must be met:

- a. Enough address-space decodes must be provided to support the necessary, probably noncontiguous, BAR spaces of the devices to be located below the PHB, including legacy devices that require an address programmed in their BARs that are below 4 GB.

- b. The address decodes must be assigned an appropriate PE#. When multiple decodes are provided for any given function, the PE# assigned must be the same.

Hardware Implementation Note: Relative to this requirement, how the hardware chooses to implement this is outside of the scope of this architecture. However, the hardware implementation must take special care relative to the configurations to be supported under the PHB, especially in terms of the implications of switches, IOV endpoints, and hot plug. Consideration must also be given to the fact that devices can implement multiple sets of BARs, and implementations generally need to allow for three, potentially noncontiguous, BARs per function.

#### R1-3.2.1.1-2 Firmware Requirement

The platform firmware must set up any chip implementation-specific address ranges appropriately.

#### **3.2.1.2. DMA and Error Message PE# Determination, RTT, RTC Invalidate, and PELT-V**

The RTT and PELT-V tables are implemented in system memory. The most recently used RTEs are cached in the PHB hardware for DMA performance and, optionally, for MSI performance. RTEs can be cached for processing of PCI error messages.

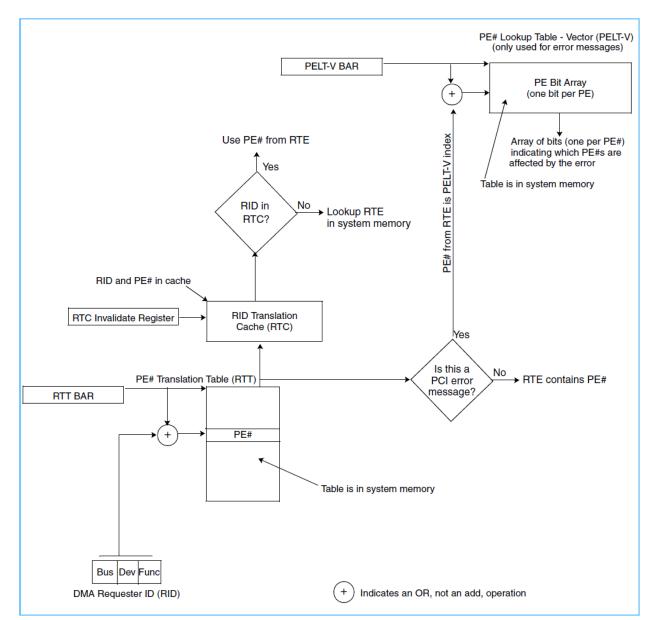

DMA operations or error messages that come from the PCIe link contain a requester ID (RID) associated with the operation. The RID is used as an index into an RID translation table (RTT). The RTT entry (RTE) contains a PE# field.

If the operation is a DMA or MSI operation, the RTE indicates the PE# associated with the RID. If the operation is an error message, the PE# field is the index of the PELT-V. When the PELT-V is accessed, the entry indicates, by a vector of bits, which PE#s are affected by the RID. PELT-V entries are generated by firmware for all PE#s. That is, the depth of the PELT-V is equal to the number of PEs implemented. Hierarchical RIDs, such as switch RIDs and IOV PFs, have more than one bit in the PELE-V set. Single RIDs, such as VFs, have only one bit set. For DMA operations and, optionally, for MSI and error message operations, the RID and PE# are stored in a cache on the PHB chip. The cache is referenced first in the PE translation process. If the entry is not in the cache, a reference is made to the RTT in system memory.

Figure 3.1, "PE# Determination for DMA and Error Messages" [9]shows how PE#s are determined for DMA and error messages. For specific hardware and firmware requirements related to this, see R1-3.2.1.2 [7]-1 and R1-3.2.1.2 [7]-2.

The RTT is 64K-entries deep because the RID, which is the index into the table, is 16 bits in length. The width and depth of the PELT-V table is determined by the number of PEs implemented, with one entry per PE and one bit width for each PE, and with the width in bytes being a power of 2.

The definitions of the RTT, RTC Invalidate Register, and PELT-V tables are shown in Table 3.1, "RTE Definition" [10], Table 3.2, "RTC Invalidate Register Definition" [10], and Table 3.3, "PELE-V Definition" [10].

In the tables, [] designates optional bits or bytes. Optional bits and bytes that are not implemented by the hardware must be ignored by the hardware. Implementations that do not implement the full size of the field must treat unused bits and bytes the same as optional bits and bytes. Reserved bits and bytes must be set as zeros by firmware and must be returned as written on a Load (these tables are in system memory).

#### Table 3.1. RTE Definition

| Bytes | Bits | Field | Definition                                                                                                                                         |

|-------|------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| 0:1   | All  | PE#   | The PE# or index into the PELT-V. A PE# of all ones is invalid. Therefore, firmware must set the PE# to all ones for RIDs that are not configured. |

#### Table 3.2. RTC Invalidate Register Definition

| Bits  | Field               | Definition                                                                                                                                                                             |  |

|-------|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 0     | Invalidate All      | <ol> <li>Invalidate the entry in the RTC specified by the Requester ID field.</li> <li>Invalidate all entries in the RTC regardless of the value in the Requester ID field.</li> </ol> |  |

| 1:15  | Reserved            | Reserved                                                                                                                                                                               |  |

| 16:31 | Requester ID (0:15) | The 16-bit Requester ID field of the RTC entry to invalidate when the Invalidate All bit is set to a zero.                                                                             |  |

| 32:63 | Reserved            | Reserved                                                                                                                                                                               |  |

#### Table 3.3. PELE-V Definition

| Bytes | Bits  | Field | Definition                                                                                                                                                                                                                                                                                                                                                               |

|-------|-------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0:[n] | [All] | 2     | An array of bits, one bit per PE, that indicates which PEs are affected. An implementation only needs to support the number of bits necessary to support the number of PEs that it supports. Unused bits are at the highest bit numbers (bit 0 of byte 0 corresponds to the first PE#, bit 1 to the second, and so on). The number of bytes implemented is a power of 2. |

#### R1-3.2.1.2-1 Hardware Requirement

The PHB hardware must take all of the following actions:

- a. Implement the RTT in system memory, with the entries defined by Table 3.1, "RTE Definition" [10], and provide a register that firmware can set to point to the starting address of that table.

- b. Implement a BAR to point to the start of the RTT (RTT BAR), loadable by the firmware.

- c. Implement the PELT-V in system memory, with entries defined by Table 3.3, "PELE-V Definition" [10], and provide a register that firmware can set to point to the starting address that table.

- d. Implement a BAR to point to the start of the PELT-V (PELT-V BAR), loadable by the firmware.

- e. Provide an RID translation cache (RTC) for caching RTEs used for DMA operations, optionally for MSI operations and for error message operations.

#### Hardware Implementation Notes:

- 1. Appropriate sizing of the RTC is necessary to have a high probability of a cache hit during DMA. Currently, no performance analysis has been done, and no rule-of-thumb can be provided. However, the target size for the first implementation of this architecture is a number of entries in the RTC equal to one-fourth of the number of PEs.

- 2. In part e of this requirement, it is best for the optional caching for MSI operations to be controllable on a per-PHB basis by a configuration bit setting.

- f. Provide an RTC Invalidate Register, as defined by Table 3.2, "RTC Invalidate Register Definition" [10], for invalidating individual cached RTEs or all RTEs. The hardware must stop using

the entry when firmware indicates the invalidate, but can wait until the RTC entry is used once by a DMA operation. A *Store* to this register must perform the specified invalidation operation. A *Load* from this register must return the last value *Stored* to this register.

#### Hardware Implementation Notes:

Relative to requirement part f, the hardware is required to provide firmware a way to clean up cache entries when they are no longer needed or when the RID to PE# might have changed. This is done during firmware clean-up operations, for example on hot plug or partition shutdown. The firmware might also need to be able to invalidate all entries in the RTC, for example if the RTC BAR is to be changed. The RTC Invalidate register format is not defined by this architecture.

- g. During RID translation, if the RID is in the RTC, use the cached value.

- h. During RID translation, if the RID is not in the RTC, use the RID as an index into the RTT for the PHB, and read the RTE. Cache the entry if this is a DMA operation, optionally cache it for MSI operations, and optionally cache it for error messages. For error messages, if the PE# is not all ones, use the PE# field in the RTE as a PELT-V index. Access the PELT-V entry and use the bit array obtained as the array of PE#s that are affected by the error.

#### **Architecture Notes**

DMAs from entities like PCIe IOV PFs, and MSIs from PFs, and switch RIDs have only one PE# associated with them. Error messages from PFs and switch RIDs are likely to point to multiple PE#s in the PELT-V.

i. When accessing the RTT, if the RTE is all ones, an invalid RID has been received. The hardware must set the appropriate error bit in the PHB, store the RID information, and interrupt the firmware for processing of the error.

#### **R1-3.2.1.2-2** Firmware Requirement:

The platform firmware must take all of the following actions:

- a. Set up the RTT BAR and PELT-V BAR to point to the start of those structures in contiguous real system memory, with a size that is a power of 2 and with an address alignment on an integer multiple of the size of the table.

- b. To change the RTT BAR or PELT-V BAR while DMA operations might be in progress, the firmware must first create the new table and change the BAR. Then, firmware must make sure that all DMA operations that are queued in the PHB (DMA write/read and MSIs) are completed before reusing the system memory locations that were previously used by the table.

- c. For RIDs that do DMA or which issue MSIs, set up the PE# in the RTT to the PE# that is associated with the RID. There might be more than one RID associated with the same PE#.

- d. For each PE#, create an entry in the PELT-V with an offset equal to the PE#. That entry must contain the appropriate bits set for each PE that might be affected by an error against the RID associated with the PE#.

- e. For invalid RIDs (that is, ones that are not configured in the PCIe hierarchy), set the RTE to all ones.

- f. Manage the RTT and PELT-V entries in system memory and the RTC on the PHB chip, appropriately, at all times, including during hot plug and DLPAR operations.

#### 3.2.1.3. PE State and EEH

The PE state includes, but is not limited to, the following items:

- The EEH Enablement state: Indicates whether EEH is enabled for the PE or not.

- The MMIO Stopped state: Indicates whether MMIO operations are frozen for the PE or not. If MMIO is stopped for the PE, the PE is said to have its MMIO Stopped state set or to be in the MMIO Stopped state.

- The DMA Stopped state: Indicates whether DMA (and MSI) operations are frozen for the PE or not. If DMA is stopped for the PE, the PE is said to have its DMA Stopped state set or to be in the DMA Stopped state.

**Note:** For EEH-enabled DDs, on the detection that their PE is in the Stopped state (all ones on a *Load* when not expected followed by a query call to firmware), the normal progression is as follows:

- 1. Remove their PE from the MMIO Stopped state (that is, reset that state).

- 2. Issue a series of *Load/Stores* to determine the problem.

- 3. Clear it either by a hardware reset to the PE or by separately removing the IOA function from the DMA Stopped state. The latter approach might not be possible for some IOA functions or under certain circumstances.

#### R1-3.2.1.3-1 Hardware Requirement:

Each PE's MMIO Stopped state and DMA Stopped state must be independent of each other. The hardware must give the firmware a way to set and clear the DMA Stopped state and the MMIO Stopped state:

- · Independently from each other

- Independent for those Stopped states for other PEs

- Atomically with any other errors that might be occurring at the time

#### R1-3.2.1.3-2 Hardware Requirement:

The PHB hardware must take all of the following actions:

a. For any detected failure to/from a PE, set both the MMIO Stopped and DMA Stopped states for the PE.

**Exception:** Not required if the error that caused the failure can be reported to the IOA function in a way that enables it to report the error to its device driver while avoiding any data corruption.

- b. If an I/O fabric consists of a hierarchy of components, when a failure is detected in the fabric and that failure cannot be isolated to a single PE, put all PEs that are downstream of the failure into the MMIO Stopped and DMA Stopped states if they might be affected by the failure.

- c. From the time that the MMIO Stopped state is entered for a PE, prevent the PE from responding to *Load* and *Store* operations including the operation that caused the PE to enter the MMIO Stopped state. A *Load* operation must return all ones with no error indication and a *Store* opera-

tion must be discarded until the firmware directs the hardware otherwise or until the PHB chip is reset. That is, *Load* and *Store* operations are treated as if they received a conventional PCI master abort error,

- d. From the time that the DMA Stopped state is entered for a PE, prevent the PE from initiating a new DMA request or completing a DMA request that caused the PE to enter the DMA Stopped state, including MSI or MSI-X DMA operations, until the firmware directs the hardware otherwise or until the PHB chip is reset. DMA requests that were started before the DMA Stopped state is entered can be completed. DMA requests requiring a response that are discarded due to the PE being in the DMA Stopped state (for example, a read request or an atomic request), return a UR to the requester. DMA read response data that is returned to the PHB after the setting of the DMA Stopped state must be returned to the requester with a Completer Abort status, if possible. Otherwise, discard the response; for example, a link down condition is a case where return of a response is not possible.

- e. Provide the capability to the firmware to determine, on a per-PE basis, that a failure occurred which caused the PE to be put into the MMIO Stopped and DMA Stopped states and to read the actual state information (MMIO Stopped state and DMA Stopped state).

- f. Provide the capability of separately enabling and resetting the DMA Stopped and MMIO Stopped states for a PE without disturbing other PEs on the platform. The hardware must provide this capability without requiring a PE reset and must do so through normal processor *Store*instructions. Firmware enabling of MMIO or DMA Stopped states must have the same, and immediate, effect as if a PHB-detected error set those states.

- g. Provide the capability to the firmware to deactivate all provided resets (hot reset, fundamental reset), independent of other resets. The hardware must provide the proper controls on the reset transitions to prevent failures from being introduced into the platform by the changing of the reset.

- h. Provide the capability to the firmware to activate all provided resets (hot reset, fundamental reset), independent of other resets. The hardware must provide the proper controls on the reset transitions to prevent failures from being introduced into the platform by the changing of the reset.

- i. When a PE is put into the MMIO Stopped and DMA Stopped states, do so in a way that does not introduce failures that might corrupt other parts of the platform.

- j. Allow firmware access to internal PHB and I/O fabric PCI configuration registers when any or all of the PEs are in the MMIO Stopped state.

#### Harware Implementation Notes:

- 1. The type of error information trapped by the hardware when a PE is placed into the MMIO Stopped and DMA Stopped states is implementation dependent and is beyond the scope of this architecture.

- 2. A DMA operation (Read or Write) that was initiated before a *Load*, *Store*, or DMA error, does not necessarily need to be blocked because it was not a result of the *Load*, *Store*, or DMA that failed. The normal PCI Express ordering rules require that an ERR\_FATAL or ERR\_NONFATAL from a failed *Store* or DMA error, or a *Load* Completion with error status must reach the PHB before any DMA that might have been kicked off in error as a result of a failed *Load* or *Store* or a *Load* or *Store* that follows a failed *Load* or *Store*. This means that as long as the PHB processes an ERR\_FATAL, ERR\_NONFATAL, or *Load* Completion that indicates a failure, before processing any more DMA operations or *Load* Completions, and puts the PE into the MMIO and Stopped DMA Stopped states, implementations can block DMA operations that were kicked off after a failing DMA operation without violating the normal PCI Express ordering rules.

### **3.2.1.4. Error-Injection Hardware Requirements**

The error-injection hardware is defined primarily to test enhanced error-recovery software. As implemented in the I/O bridge, this option is used to test the software that implements the recovery that is enabled by the EEH option in that bridge. Specifically, the PAPR *ioa-bus-error* and *ioa-bus-error-64* functions of the *ibm,errinjct* RTAS call are used to inject errors onto each PE primary bus. This, in turn, causes certain actions on the bus and certain actions by the PE, the EEH logic, and by the error recovery software.

The type of errors and the injection qualifiers place the following additional requirements on the hardware for this option.

#### R1-3.2.1.4-1 Hardware Requirement:

The PHB hardware must take all of the following actions:

- a. Provide a way to inject the required errors for each PE primary bus. The errors must be injectable independently without affecting the operations on the other buses in the platform.

- b. Provide a way to set up for the injection of the required errors without disturbing operations to other buses outside the PE.

- c. Provide firmware with a way to set up the following information for the error injection operation by normal processor *Load* and *Store* instructions:

- · Address at which to inject the error

- Address mask to mask off any combination of the least-significant 24 (64 for the *ioa-bus-er-ror-64* function) bits of the address

- PE primary bus number that is to receive the error

- Type of error to be injected

- d. Provide the capability of selecting the errors specified in Table 3.4, "Supported Errors for PCI Express Error Injectors" [14]and an indication of when that error is appropriate for the platform configuration.

- e. Provide a way to inject the errors in Table 3.4, "Supported Errors for PCI Express Error Injectors" [14]in a non-persistent manner (that is, at most one injection for each invocation of the *ibm,errinjct* RTAS call).

#### R1-3.2.1.4-2 Firmware Requirement:

The firmware must limit the injection of errors that are inappropriate for the given platform configuration.

#### Table 3.4. Supported Errors for PCI Express Error Injectors

| Operation | PCI Address Spaces  | Errors         | Other Requirements                                                                                      |

|-----------|---------------------|----------------|---------------------------------------------------------------------------------------------------------|

| Load      | Memory, I/O, Config | TLP ECRC Error | The TLP ECRC covers the address and data bits of a TLP.                                                 |

| Store     | Memory, I/O, Config | TLP ECRC Error | Therefore, you cannot determine if the integrity error resides in the address or data portion of a TLP. |

| Operation | PCI Address Spaces | Errors                                    | Other Requirements                                                                                                                                                    |

|-----------|--------------------|-------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DMA Read  | Memory             | TLP ECRC Error                            | The TLP ECRC covers the address and data bits of a TLP.<br>Therefore, you cannot determine if the integrity error resides in<br>the address or data portion of a TLP. |

|           |                    | Completer Abort or<br>Unsupported Request | Inject the error that is injected on a TCE page fault.                                                                                                                |

| DMA Write | Memory             | TLP ECRC Error                            | The TLP ECRC covers the address and data bits of a TLP.<br>Therefore, you cannot determine if the integrity error resides in<br>the address or data portion of a TLP. |

### **3.2.2. DMA Design, TVEs, and TCEs**

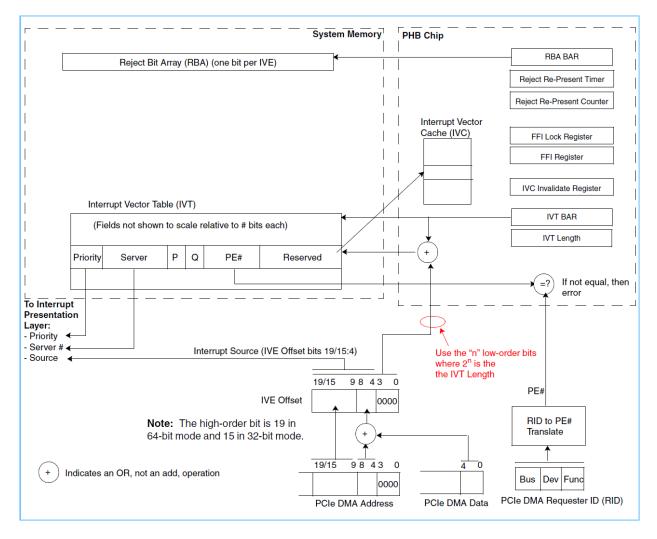

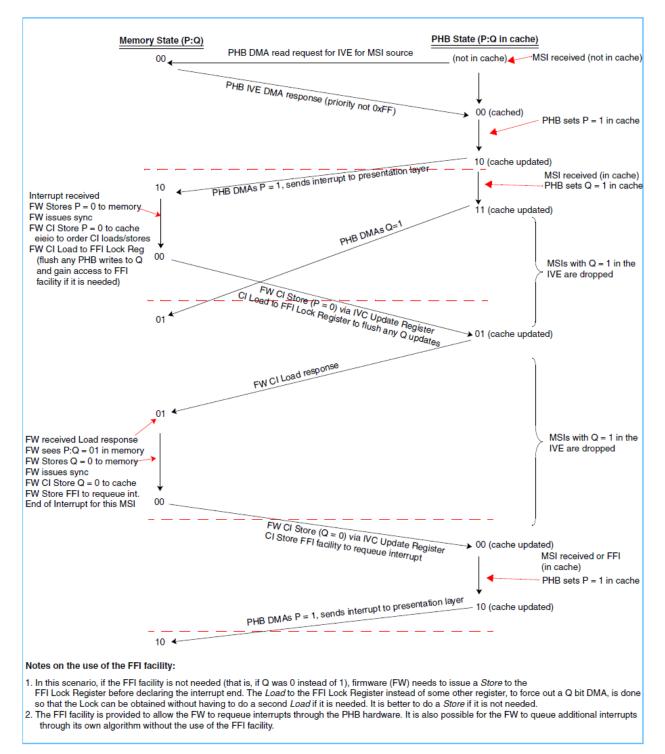

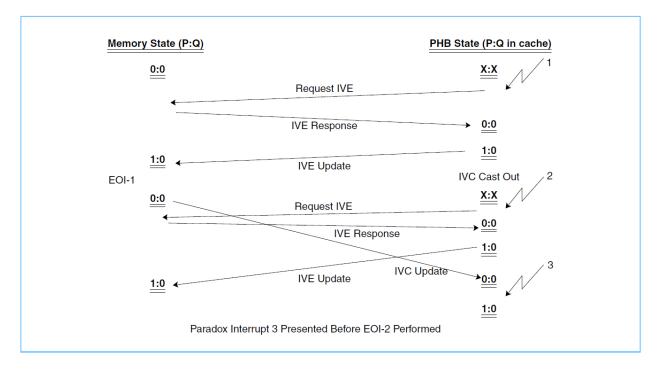

This section describes the constructs for DMA operations, except when those DMA operation are for MSI. For 64-bit MSI operations, the bits 61:60 in the address are set to 0b01. For 32-bit MSI operations, the bits 31:16 are set to 0xFF. For information about MSI operations, see Section 3.2.4, "MSI Design" [35].

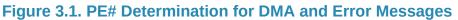

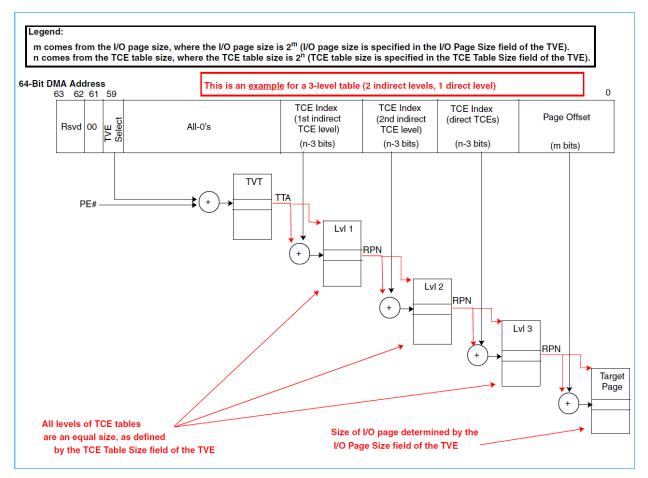

The DMA address for non-MSI operations (that is, for normal DMA operations), is broken up into fields as shown in Figure 3.2, "PCIe Non-MSI DMA Operation Address Fields" [15]. The size of the fields in the address, the number of levels of a TCE table (in the case of the multilevel TCE table), the I/O page size, and the TCE table size are defined by the fields of the TVE (see Table 3.5, "TVE Definition" [23]).

#### Figure 3.2. PCIe Non-MSI DMA Operation Address Fields

Figure 3.2, "PCIe Non-MSI DMA Operation Address Fields" [15]shows that multiple levels of TCE tables are possible (that is, multiple TCE index levels are shown). Details of single-level tables, for which there exists only the final (direct TCE level) table, are shown in the following sections:

• Section 3.2.2.1, "DMA Design Details: No Page Migration" [16].

• Section 3.2.2.2, "Additional DMA Design Details: Page Migration" [25].

The differences for multilevel tables are described in Section 3.2.2.3, "Additional DMA Design Details: Multilevel TCE Tables" [30].

### **3.2.2.1. DMA Design Details: No Page Migration**

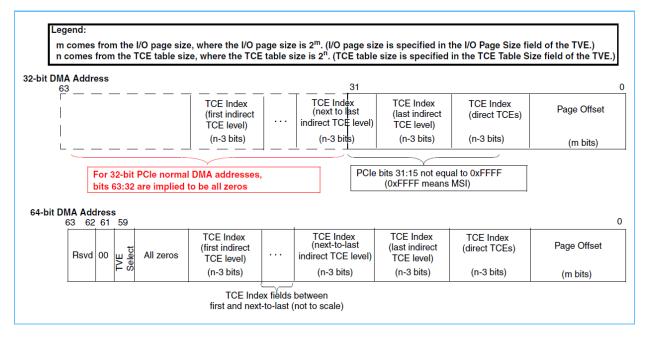

Figure 3.3, "DMA Operation High-Level Diagram - No Page Migration" [16]shows the general flow of an I/O DMA operation through the system: the address validation, address translation (via TCEs), and caching of the TCEs and data. The description of this figure follows the figure.

#### Figure 3.3. DMA Operation High-Level Diagram - No Page Migration

Referring to Figure 3.3, "DMA Operation High-Level Diagram - No Page Migration" [16]:

- 1. The IOA function places the DMA address and RID on the I/O bus.

- The low-order bits indicate the offset into the page (the page offset). For example, for 4K pages, this is the low-order 12 bits.

- The bits immediately above the Page Offset are the index into the TCE table (TCE Index). The number of TCE Index bits is determined by the size of the TCE table (that is, the number of TCEs) that is accessible by the RID (not the total size of the TCE table).

- The RID ties the requester to a particular PE#.

- 2. The PE# is determined from lookup in the RTC. If it is not in the RTC, it is accessed from the RTT and placed in the RTC.

- 3. If the PE# is in the DMA Stopped state, abort the operation (see Section 3.2.1.3, "PE State and EEH" [12]).

- If the operation is a DMA Read Request, return a UR error to the requester.

- If the operation is a DMA Write, discard the data.

- 4. The PE# and one or more high-order address bits are used to access the correct TVE for the PE.

- Bit 59 is used at a minimum. Implementations can allow more bits to be used as an option (for example, bit 59 or bits 59:55). PHBs operate bi-modally relative to the whole PHB, using either one bit or more than one bit, but not both (operation with bit 59 is required).

- 32-bit DMAs are essentially 64-bit DMAs with the high-order 32-bits set to all zeros. Therefore, for the purpose of TVE selection, all zeros are used for the address selection bits. Thus, only one TVE is available for addresses below 4G.

- 5. The DMA address is validated to make sure that the RID is allowed to access that I/O bus address. Otherwise, the operation is denied to the IOA function. This is done by the parameters in the TVE in one of two ways:

- For translate mode, the I/O Page Size and the TCE Table Size are used.

- For no-translate mode, the address range for no-translate, a base/bounds, is used. See also Appendix B, No-Translate Operation [57].

- 6. A determination is made about the address of the TCE translation table (TTA from the TVE) to be used to translate the address and the route to the TCE table.

#### Note

This step might follow the next step (determination of whether TCE is already cached) in some implementations.

7. A determination is made about whether the needed TCE is already cached. The caching algorithm must take into consideration the I/O Page Size.

- 8. If the TCE is not already cached, it is fetched. If it is valid for the operation, it is cached.

- In the following cases, abort the operation and set the MMIO and DMA Stopped states for the PE:

- The TCE is invalid (the read-valid and write-valid Page Mapping and Control bits are both 0).

- The operation is a write and the write-valid bit is off.

- The operation is a read and the read-valid bit is 0.

- 9. The PCIe bus address is translated using the information from the TCE and the DMA bus address.

- The address is translated by using the page offset from the DMA bus address as the low-order bits of the translated address in the TCE.

#### Note

The number of page offset bits is determined by the I/O Page Size. The I/O Page Size is specified in the I/O Page Size field of the TVE (see Table 3.5, "TVE Definition" [23]).

• The high-order bits are obtained from the Real Page Number (RPN) in the TCE.

For more information, see:

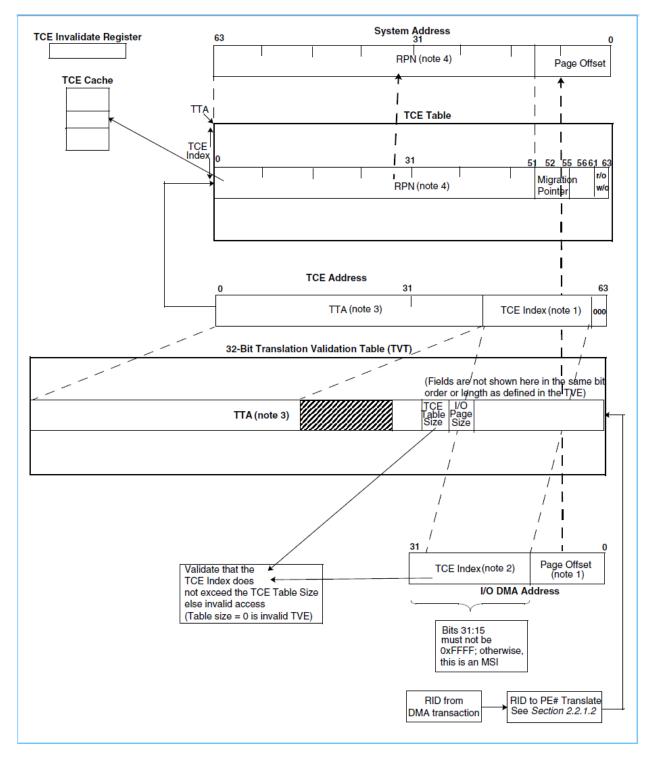

- Figure 3.4, "I/O Address Validation and TCE Translation Implementation for 32-Bit DMA Addresses" [19], which shows how the translation from I/O address to system memory address works for 32-bit I/O addresses

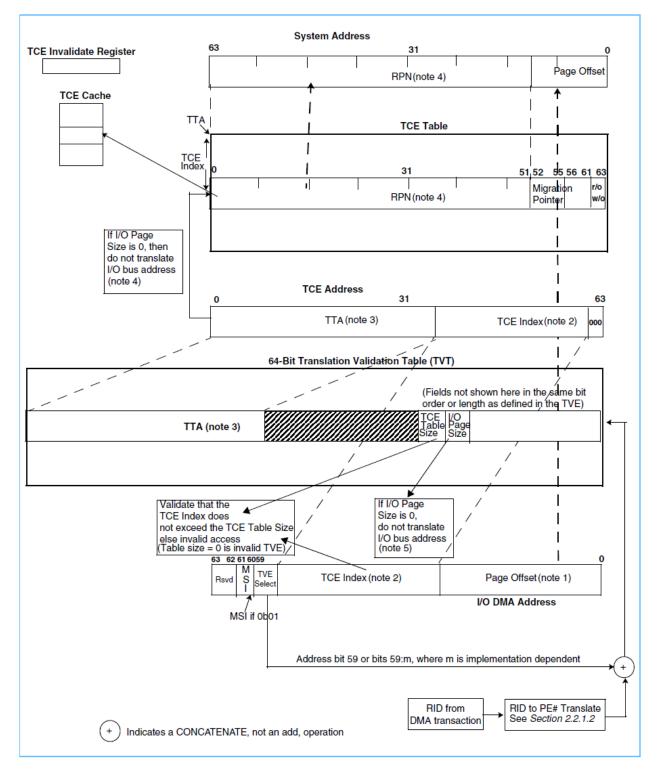

- Figure 3.5, "I/O Address Validation and TCE Translation Implementation for 64-Bit DMA Addresses" [21], which shows how the translation from I/O address to system memory address works for 64-bit I/O addresses

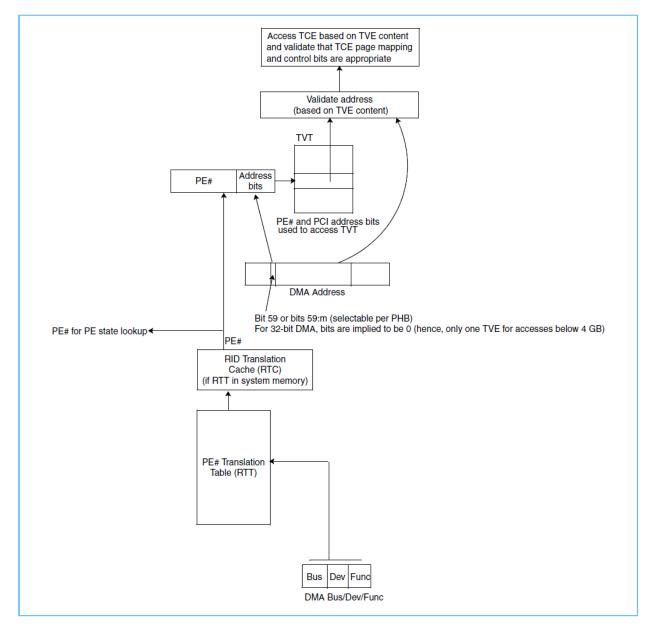

# Figure 3.4. I/O Address Validation and TCE Translation Implementation for 32-Bit DMA Addresses

Notes on Figure 3.4, "I/O Address Validation and TCE Translation Implementation for 32-Bit DMA Addresses" [19]and Figure 3.5, "I/O Address Validation and TCE Translation Implementation for 64-Bit DMA Addresses" [21]:

- 1. The Number of Page Offset bits is determined by the I/O Page Size. That is, the boundary between the TCE Index field and the Page Offset field slides right and left depending on the I/O Page Size. This architecture does not require hardware verification of I/O page sizes of anything other than 4 KB for 32-bit DMA operations (that is, for DMAs with an address less than 4 GB).

- 2. The TCE Index field size is based on the number of pages to which the IOA function has access.

- 3. The Number of TTA bits used in the least-significant bits is determined by the TCE Index field size. The number of TTA bits implemented in the most-significant bits is dependent on the maximum size of system memory to be supported by the platform.

- 4. The number of most significant RPN bits implemented in the TCE is dependent on the maximum size of system memory to be supported by the platform. The number of least significant RPN bits used depends on the number of Page Offset bits (that is, on the size of the page mapped by the TCE, as determined from the I/O Page Size field in the TVE). Also, if the I/O Page Size is zero in the TVE, the I/O Bus Address is used untranslated to access the system. For more information, see the definition for the "Address range for no translate" field in Table 3.5, "TVE Definition" [23].

- 5. An implementation can choose to check that the DMA address bits (63:62) are 0b00, that bits 61:60 are not 0b10 or 0b11, and that unused TVE select bits (per mode) are all zero. If any of these conditions are not true, an implementation can choose to abort the operation and set the MMIO and DMA Stopped states for the PE. However, the implementation is not required to do so.

# Figure 3.5. I/O Address Validation and TCE Translation Implementation for 64-Bit DMA Addresses

When the TVE entry has an I/O Page Size other than zero, the TVE associates a DMA address range, which is based on the high-order address bits used with the PE# to select the TVE, with a TCE table starting address (TTA), TCE table size, and an I/O page size. When the TVE entry has an I/O Page Size of zero, TCE translation is not performed, and the TTA field becomes an address range check.

#### R1-3.2.2.1-1 Hardware Requirement:

The PHB hardware must take all of the following actions:

- a. Implement the TVE table, as defined by Table 3.5, "TVE Definition" [23], with the TVT being located on the PHB chip.

- b. Implement the TCE table, with entries as defined by Table 3.6, "TCE Definition" [24], with the TCE table being in system memory and cached on the PHB chip.

- c. Provide a TCE Invalidate Register, as defined in Table 3.7, "TCE Invalidate Register Definition" [25], for invalidating cached TCEs, all TCEs for a particular PE, or the entire cache of TCEs. The hardware must stop using the entry when firmware indicates the invalidate, but it can wait until the TCE is used once by a DMA operation. A *Store* to this register causes the specified operation. Issuing a *Load* to this register causes the last value *Stored* to be returned.

- d. Implement the DMA flows as shown in Figure 3.3, "DMA Operation High-Level Diagram No Page Migration" [16], Figure 3.4, "I/O Address Validation and TCE Translation Implementation for 32-Bit DMA Addresses" [19], and Figure 3.5, "I/O Address Validation and TCE Translation Implementation for 64-Bit DMA Addresses" [21].

#### R1-3.2.2.1-1 Firmware Requirement:

The firmware must take all of the following actions:

- a. Set up the TVEs appropriately.

- b. Access the TVE table with 8-byte *Loads* and *Stores*, naturally aligned.

- c. Set up the TCEs appropriately.

- d. Maintain the coherency between the system memory TCE value and the cached TCE value by using the TCE Invalidate Register to invalidate cached TCEs whenever it changes the value of a TCE.

In Table 3.5, "TVE Definition" [23], [] designates optional bits and bytes. Optional bits and bytes that are not implemented must be ignored by that implementation on a *Store* and must be returned as zeros on a *Load*, even when the entire field is not implemented. Implementations that do not implement the full size of the field must treat unused bits and bytes the same as optional bits and bytes. Reserved bits and bytes must be ignored on a *Store* and must be returned as zeros on a *Load*.

#### Note

A nonzero TCE Table Size field indicates a valid TVE.

#### Table 3.5. TVE Definition

| Bytes | Bits | Field                                       | Definition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-------|------|---------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0:5   | All  | TTA<br>or<br>Address range for no translate | When the I/O Page Size field is nonzero and the TVE is valid (TCE Table Size is nonzero), this field is the TCE Table Address (TTA). Bit 0 of the TVE aligns with system address bit 4, bit 1 with system address bit 5, and so on. TCE tables must be aligned on a boundary that is an integer multiple of their size, and, therefore, depend on the size of the table and the TCE size. Some of the low-order bits of this field might not be needed and must be set to zero by the software. Hardware pads this field with zeros, if necessary, in the case of large I/O page sizes where the TCE table is smaller than 4 KB. Likewise, only enough high-order bits need to be implemented by the hardware to match the largest real address in the platform. The minimum alignment is at least 4 KB. |

|       |      |                                             | When the I/O Page Size field is zero (no translate case) and the TVE is valid (TVE[byte 6, bit 3] = 1), then if                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|       |      |                                             | PCI Express address [bits $49:24$ ] $\geq$ (TVE[byte 6, bits 4:5] concatenated with TVE[bytes 0:2])                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|       |      |                                             | and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|       |      |                                             | PCI Express address [bits 49:24] < (TVE[byte 6, bits 6:7] concatenated with TVE[bytes 3:5]),                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|       |      |                                             | then use the PCI Express address [bits 49:0], untranslated, as the DMA address.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|       |      |                                             | Notes:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|       |      |                                             | 1. The no-translate case is not valid for 32-bit PCI Express addresses.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|       |      |                                             | 2. The no translate and translate cases have different alignment require-<br>ments. For the translate case, the size of the area translated by the TCE<br>table dictates the alignment requirements; it must be aligned on an integer<br>multiple of the size. However, for the no translate case, the alignment is 16<br>MB or larger.                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|       |      |                                             | 3. See also Appendix B, No-Translate Operation [57].                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 6     | 0:2  | Number of TCE Table Levels                  | This field indicates the number of indirect TCE table levels for operations using this TVE, which is the total number of TCE table levels (including the last level) minus 1. When this field is zero, there are no indirect levels. See also Section 3.2.2.3, "Additional DMA Design Details: Multilevel TCE Tables" [30].                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|       |      |                                             | The following values are defined by this architecture:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|       |      |                                             | 000 - Only one level (direct level)<br>001 - One indirect level, one direct level<br>010 - Two indirect levels, one direct level<br>011 - Three indirect levels, one direct level<br>100 - Four indirect levels, one direct level<br>101-111 Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 6     | 3:7  | TCE Table Size                              | A value of zero in this field indicates that the TVE is invalid.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|       |      |                                             | When the I/O Page Size field is nonzero (translate case) and the TVE is valid (that is, this field is nonzero), the value of this field defines the number of DMA I/O bus address bits that are used for the TCE index field or fields (see Figure 3.2, "PCIe Non-MSI DMA Operation Address Fields" [15]). The hardware uses the value of this field, along with the Number of TCE Table Levels and I/O Page Size fields of this TVE, to validate the range of the DMA I/O address. That is, it validates that the appropriate number of high-order bits in the DMA I/O bus address are zero. It also uses the value of this field to prevent an IOA function from accessing outside of its address range.                                                                                               |

|       |      |                                             | Value of 0: Invalid TVE<br>Value of 1: 9 TCE Index bits, 4 KB table size<br>Value of 2: 10 TCEIndex bits, 8 KB table size                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Bytes | Bits  | Field         | Definition                                                                                                                                                         |

|-------|-------|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       |       |               | Value of 3: 11 TCEIndex bits, 16 KB table size                                                                                                                     |

|       |       |               | Value of 4: 12 TCEIndex bits, 32 KB table size                                                                                                                     |

|       |       |               | Value of 5: 13 TCEIndex bits, 64 KB table size                                                                                                                     |

|       |       |               | Value of 6: 14 TCEIndex bits, 128 KB table size                                                                                                                    |

|       |       |               | Value of 7: 15 TCEIndex bits, 256 KB table size                                                                                                                    |

|       |       |               | Value of 8: 16 TCEIndex bits, 512 KB table size                                                                                                                    |

|       |       |               | Value of 9: 17 TCEIndex bits, 1 MB table size                                                                                                                      |

|       |       |               | Value of 10: 18 TCEIndex bits, 2 MB table size                                                                                                                     |

|       |       |               | Value of 11: 19 TCEIndex bits, 4 MB table size                                                                                                                     |

|       |       |               | Value of 12: 20 TCEIndex bits, 8 MB table size                                                                                                                     |

|       |       |               | Value of 13: 21 TCEIndex bits, 16 MB table size                                                                                                                    |

|       |       |               | Value of 14: 22 TCEIndex bits, 32 MB table size                                                                                                                    |

|       |       |               | Value of 15: 23 TCEIndex bits, 64 MB table size                                                                                                                    |

|       |       |               | Value of 16: 24 TCEIndex bits, 128 MB table size                                                                                                                   |

|       |       |               | Value of 17: 25 TCE Index bits, 256 MB table size                                                                                                                  |

|       |       |               | Value of 18: 26 TCE Index bits, 512 MB table size                                                                                                                  |

|       |       |               | Value of 19: 27 TCE Index bits, 1 GB table size                                                                                                                    |

|       |       |               | Value of 20: 28 TCE Index bits, 2 GB table size                                                                                                                    |

|       |       |               | Value of 21: 29 TCE Index bits, 4 GB table size                                                                                                                    |

|       |       |               | Value of 22: 30 TCE Index bits, 8 GB table size                                                                                                                    |

|       |       |               | Value of 23: 31 TCE Index bits, 16 GB table size                                                                                                                   |

|       |       |               | Value of 24: 32 TCE Index bits, 32 GB table size                                                                                                                   |

|       |       |               | Value of 25: 33 TCE Index bits, 64 GB table size                                                                                                                   |

|       |       |               | Value of 26: 34 TCE Index bits, 128 GB table size                                                                                                                  |

|       |       |               | Value of 27: 35 TCE Index bits, 256 GB table size                                                                                                                  |

|       |       |               | Value of 28: 36 TCE Index bits, 512 GB table size                                                                                                                  |

|       |       |               | Value of 29: 37 TCE Index bits, 1 TB table size                                                                                                                    |

|       |       |               | Value of 30: 38 TCE Index bits, 2 TB table size                                                                                                                    |

|       |       |               | Value of 31: 39 TCE Index bits, 4 TB table size                                                                                                                    |

|       |       |               | When the I/O Bage Size field is zero (no translate eace) and the TVE is valid                                                                                      |

|       |       |               | When the I/O Page Size field is zero (no translate case) and the TVE is valid (that is, this field is non-zero), this indicates that the TVE bytes [0:5] are to be |

|       |       |               | used to validate the PCI Express address (see the definition for the "Address                                                                                      |