# POWER9<sup>™</sup> Processor Programming Model Bulletin

September 9, 2019

The specifications in this bulletin are subject to change without notice. Periodic changes to this publication may be incorporated in new additions or supplements to this publication. This publication is provided "AS IS" and IBM Corporation makes no warranty of any kind, expressed or implied, including, but not limited to, the implied warranties of merchantability and fitness for a particular purpose.

IBM® and POWER® are trademarks of IBM Corp., registered in many jurisdictions worldwide.

This material contains some concepts that were developed during research sponsored by the Department of Homeland Security (DHS) Science and Technology Directorate, Cyber Security Division (DHS S&T/CSD) via BAA 11-02; the Department of National Defense of Canada, Defense Research and Development Canada (DRDC); and Air Force Research Laboratory Information Directorate via contract number FA8750-12-C-0243. The U.S. Government and the Department of National Defense of Canada, Defense Research and Development Canada (DRDC) are authorized to reproduce and distribute reprints for Governmental purposes notwithstanding any copyright notation thereon. The views and conclusions contained herein are those of the authors and should not be interpreted as necessarily representing the official policies or endorsements, either expressed or implied, of the Department of Homeland Security; Air Force Research Laboratory; the U.S. Government; or the Department of National Defense of Canada, Defense Research Laboratory; the U.S. Government; or the Department of National Defense of Canada, Defense Research Laboratory; the U.S. Government; or the Department of National Defense of Canada, Defense Research and Development Canada (DRDC)

© Copyright International Business Machines Corporation, 1994, 2019. All rights reserved.

## **POWER9 Processor Programming Model Bulletin**

## Summary

Some members of the POWER9 Processor family implement the Protected Execution Facility. Together with the Protected Execution Ultravisor and corequisite customizations in the hypervisor (e.g. KVM), the Facility enables the creation of partitions whose memory cannot be accessed by other partitions or by the hypervisor. Hypervisor customizations are for such things as launching a protected partition and providing memory for the ultravisor and protected partitions. The integrity of the protected partitions is not dependent on the hypervisor customizations. The operation of the Facility complies with the architecture for the Secure Memory Facility, a new component of the Power ISA which is described in the following pages. The description is in the form of an RFC (Request for Change) to the Power ISA. The RFC will be included in v3.0C of the Power ISA.

## **RFC02487: Secure Memory Facility**

Date: August 29, 2019 Target Version: 3.0C Source Version: 2.07B/3.0 Books and sections affected: Book 1: Section 2.7 System Call Instructions Section 3.3.20 Move To/From System Register Instructions Book 2: Section 1.6.4 Guarded Section 5.3.1 Causes of Transaction Failure Section 5.3.2 Recording of Transaction Failure Section 5.4.2 Transaction EXception And Status Register Section 5.4.3 Transaction Failure Instruction Address Register (TFIAR) Book 3S: Section 1.2.1 Definitions and Notation Section 1.4 Exceptions Section 2.2 Logical Partitioning Control Register (LPCR) Section 2.5 Processor Compatibility Register (PCR) Section 2.7 Sharing Hypervisor and Ultravisor Resources Section 2.10 Hypervisor Interrupt Little-Endian (HILE) Bit Chapter 2+ Ultravisor and Secure Memory Facility (SMF) Section 3.2.1 Machine State Register Section 3.2.2 State Transitions Associated with the Transactional Memory Facility Section 3.2.3 Processor Stop Status and Control Register (PSSCR) Section 3.3.1 System Linkage Instructions Section 3.3.2 Power-Saving Mode Section 3.3.2.1 Power-Saving Mode Instruction Section 3.3.2.2 Entering and Exiting Power-Saving Mode Section 4.3.10 Software-use SPRs Section 4.4.5 Move To/From System Register Instructions Section 5.3.2 Address Wrapping Combined with Changing MSR Bit SF Section 5.7.3 Ultravisor Real, Hypervisor Real, and Virtual Real Addressing Modes Section 5.7.3.1 Ultravisor/Hypervisor Offset Real Mode Address

Section 5.7.3.2 Storage Control Attributes for Accesses in Ultravisor and Hypervisor Real Addressing Modes Section 5.7.3.2.1 Hypervisor Real Mode Storage Control Section 5.7.4 Definitions Section 5.7.5 Address Ranges Having Defined Uses Section 5.7.6.1 Partition Table Section 5.7.14 Storage Protection Section 5.7.14.5+ Secure Memory Protection Section 5.9.2 Synchronize Instruction Section 5.10 Page Table Update Synchronization Requirements 6.2.2+ Ultravisor Machine Status Save/Restore Registers Section 6.2.12 Hypervisor Facility Status and Control Register Section 6.3 Interrupt Synchronization Section 6.4 Interrupt Classes Section 6.4.1 Precise Interrupt Section 6.4.3 Interrupt processing Section 6.4.4 Implicit alteration of HSRR0 and HSRR1 Section 6.5 Interrupt Definitions Section 6.5.1 System Reset Interrupt Section 6.5.3 Data Storage Interrupt (DSI) Section 6.5.5 Instruction Storage Interrupt (ISI) Section 6.5.9 Program Interrupt Section 6.5.14 System Call Interrupt Section 6.5.15 Trace Interrupt Section 6.5.16 Hypervisor Data Storage Interrupt (HDSI) Section 6.5.17 Hypervisor Instruction Storage Interrupt (HISI) Secction 6.5.18 Hypervisor Emulation Assistance Interrupt Section 6.5.27+ Directed Ultravisor Doorbell Interrupt Section 6.7.2 Ordered Exceptions Section 6.9 Interrupt Priorities Section 8.3 Completed Instruction Address Breakpoint Section 8.4 Data Address Watchpoint Section 10.1 Overview Section 10.2 Programming Model Section 10.3.1 Directed Privileged Doorbell Exception State Section 10.4 Processor Control Instructions

Chapter 11. Synchronization Requirements for Context Alterations

Book Appendices:

Appendix G. Opcode Maps

Appendices H, I, J. Power ISAAS Instruction Set

#### Summary:

Adds support for the secure memory facility (SMF) security feature including creation of a new ultravisor privilege mode, checking of a secure property for each page of system memory, ultravisor interception of interrupts from secure partitions for protection of processing state, and ultravisor messages.

## Motivation

System software, including both operating system and hypervisor, comprises millions of lines of code developed by large and often disparate teams of programmers. While these components are responsible for isolating executables as well as entire virtual machines from one another to protect sensitive information, they are themselves exposed to security vulnerabilities. In order to provide protection that is independent of the security of these large system components, the secure memory facility (SMF) is added to the processor design. The SMF is implemented in hardware plus a software component that runs at a privilege level above hypervisor privilege.

This RFC provides support for coarse-grained security - preventing the hypervisor from observing the data of secure partitions.

## Changes to the Books

Please consider that this RFC was started before v3.0 was published. As a result, there are varying vintages of architecture excerpts present. Please focus on the actual changes, and not the surrounding material.

Some of the changes described herein have nothing to do with SMF.

Editorial Note: There are a large number of random places where urfid, URMOR, and either non-ultravisor or ultravisor-privileged will need to be added to existing text for completeness. Most such cases are deliberately not shown in the RFC to avoid inflating the size to be even more unwieldy.

## Book 1:

Instructions

I

#### Section 2.7 System Call Instructions

This section mentions that LEV > 1 for **sc** argument is reserved. We are using LEV = 2 for ultravisor calls. In the description of the **sc** instruction, change the third paragraph.

----- Begin text -----

The use of the LEV field is described in Book III. In the first form of the instruction the LEV values greater than 2 are reserved, and bits 0:4 of the LEV field (instruction bits 20:24) are treated as a reserved field.

------ End text -----

## Section 3.3.20 Move To/From System Register

For mtspr, add pointer to book 3 for details of loading TEXASR.

```

------Begin text ------

n ← spr<sub>5:9</sub> || spr<sub>0:4</sub>

switch (n)

case(13): see Book III

case(130): see Book III

case(808, 809, 810, 811):

default:

if length(SPR(n)) = 64 then

SPR(n) ← (RS)

else

SPR(n) ← (RS)<sub>32:63</sub>

```

The SPR field denotes a Special Purpose Register, encoded as shown in the table below. If the SPR field contains a value from 808 through 811, the instruction specifies a reserved SPR, and is treated as a no-op; see Section 1.3.3, "Reserved Fields, Reserved Values, and Reserved SPRs". Otherwise, unless the SPR field contains 13 or 130 (denoting the AMR or the TEXASR), the contents of register RS are placed into the designated Special Purpose Register. For Special Purpose Registers that are 32 bits long, the low-order 32 bits of RS are placed into the SPR.

The AMR (Authority Mask Register) is used for "storage protection." This use, and operation of *mtspr* for the AMR, are described in Book III.

The TEXASR (Transaction Exception and Status Register) is used in the analysis of transaction failures, as described in <crossref to bk2 ch5>. The operation of *mtspr* for the TEXASR is described in Book III.

----- End text -----

For mfspr, add pointer to book 3 for details of reading TEXASR.

```

-----Begin text -----

n ← spr<sub>5:9</sub> || spr<sub>0:4</sub>

switch (n)

case(129): see Book III

case(130): see Book III

```

```

case(808, 809, 810, 811):

default:

if length(SPR(n)) = 64 then

RT ← SPR(n)

else

RT ← <sup>32</sup>0 || SPR(n)

```

The SPR field denotes a Special Purpose Register, encoded as shown in the table below. If the SPR field contains 129, the instruction references the Transaction Failure Instruction Address Register (TFIAR) and the result is dependent on the privilege with which it is executed. See Book III. If the SPR field contains a value from 808 through 811, the instruction specifies a reserved SPR, and is treated as a no-op; see Section 1.3.3, "Reserved Fields, Reserved Values, and Reserved SPRs". Otherwise, unless the SPR field contains 130 (denoting the TEXASR), the contents of the designated Special Purpose Register are placed into register RT. For Special Purpose Registers that are 32 bits long, the low-order 32 bits of RT receive the contents of the Special Purpose Register and the highorder 32 bits of RT are set to zero.

The TEXASR (Transaction Exception and Status Register) is used in the analysis of transaction failures, as described in <crossref to bk2 ch5>. The operation of *mfspr* for the TEXASR is described in Book III.

----- End text ------

Book 2:

#### Section 1.6.4 Guarded

Fix the second paragraph to deal with radix and SMF.

----- Begin text -----

Except in ultravisor or hypervisor real addressing mode, instructions are not fetched from storage that is Guarded. Except in these addressing modes, if the instruction addressed by the current instruction address is in such storage, the system instruction storage error handler may be invoked (see Section 6.5.5 of Book III).

----- End text -----

### Section 5.3.1 Causes of Transaction Failure

Add that urfid, msgsndu and msgclru are disallowed.

Execution of the following instructions while in the Transactional state: *icbi, copy, paste[.], cp\_abort, lwat, Idat, stwat, stdat, dcbf, dcbi, dcbst, rfscv, rfid, hrfid, urfid, rfebb, mtmsr[d], msgsnd, msgsndp, msgsndu, msgclr, msgclrp, msgclru, slbie[g], slbia, slbmte, slbfee, stop, and tlbie[l]. (These instructions are considered to be <i>disallowed* in Transactional state.) The disallowed instruction is not executed; failure handling occurs before it has been executed.

----- End text -----

### Section 5.3.2 Recording of Transaction Failure

Add the secure bit.

----- Begin text -----

When transaction failure occurs, information about the cause and circumstances of failure are recorded in SPRs associated with the transactional facility. Failure recording is performed a single time per transaction that fails, controlled by the state of the TEXASR failure summary (FS) bit; when 0, FS indicates that failure recording has not already been performed, and is therefore permissible.

The following RTL function specifies the actions taken during the recording of transaction failure:

```

\begin{array}{l} \text{TEXASR}_{\text{Privilege}} \leftarrow \text{MSR}_{\text{HV}} \mid \mid \text{MSR}_{\text{PR}} \\ \text{TFIAR}_{\text{Privilege}} \leftarrow \text{MSR}_{\text{HV}} \mid \mid \text{MSR}_{\text{PR}} \\ \text{if } \text{MSR}_{\text{PR}} = 0 \text{ then} \\ \text{TEXASR}_{\text{Secure}} \leftarrow \text{MSR}_{\text{S}} \\ \text{TEXASR}_{\text{FS}} \leftarrow 1 \\ \text{TDOOMED} \leftarrow 1 \end{array}

```

When failure recording occurs, the TEXASR and TFIAR SPRs are set indicating the source of failure. When possible, TFIAR is set to the effective address of the instruction that caused the failure, and TEXASR<sub>37</sub> is set to 1 indicating that the contents of TFIAR are exact. When the instruction address is not known exactly, an approximate value is placed in TFIAR and TEXASR<sub>37</sub> is set to 0. TEXASR bits 0:31 are set indicating the cause of the failure, and the TEXASR<sub>Suspended</sub>, TEXASR<sub>Privilege</sub>, and TFIAR<sub>Privilege</sub> fields are set indicating the machine state in which the failure was recorded. If MSR<sub>PR</sub>=0, TEXASR<sub>Secure</sub> is also set indicating the machine state in which the failure was recorded. TEXASR<sub>TL</sub> is unchanged. The TDOOMED bit is set to 1.

#### - Programming Note

TFIAR is intended for use in the debugging of transactional programs by identifying the source of transaction failure. Because TFIAR may not always be set exactly, software should test TEXASR<sub>37</sub> before use; if zero, the contents of TFIAR are an approximation.

# Section 5.4.2 Transaction EXception And Status Register

----- End text ------

Add bit 40 to hold a copy of MSR[S].

------ Begin text ------

39 Reserved

40 Secure (S)

The thread was in Secure state when the failure was recorded.

#### — Programming Note —

This bit is read and written only when  $MSR_{PR}=0$ . When  $MSR_{PR}=1$ , *mtspr* instructions and transaction failure do not modify the bit, and *mfspr* instructions return 0 for the bit.

41:51 Reserved

#### 52:63 Transaction Level (TL)

Transaction level (nesting depth + 1) for the active transaction, if any; otherwise 0 if the most recently executed transaction completed successfully, or the transaction level at which

the most recently executed transaction failed if the most recently executed transaction did not complete successfully.

#### Programming Note

A value of 1 corresponds to an outer transaction. A value greater than 1 corresponds to a nested transaction.

The transaction level in TEXASR<sub>TL</sub> contains an unsigned integer indicating whether the current transaction is an outer transaction, or is nested, and if nested, its depth. The maximum transaction level supported by a given implementation is of the form  $2^{t}$  - 1. The value of *t* corresponding to the smallest maximum is 4; the value of *t* corresponding to the largest maximum is 12. This value is tied to the "Maximum transaction level" parameter useful for application programmers, as specified in Section 4.1. The high-order 12-*t* bits of TEXASR<sub>TL</sub> are treated as reserved.

Transaction failure information is contained in TEX-ASR<sub>0:3740</sub>. The fields of TEXASR are initialized upon the successful initiation of a transaction from the Nontransactional state, by setting TEXASR<sub>TL</sub> to 1, indicating an outer transaction, and all other fields to 0.

When transaction failure is recorded, the failure summary bit TEXASR<sub>ES</sub> is set to 1, indicating that failure has been detected for the active transaction and that failure recording has been performed. TEXASR<sub>0:31</sub> are set indicating the source of the failure. Exactly one of bits 8 through 31 will be set indicating the instruction or event that caused failure. In the event of failure due to the execution of a tabort., tabortdc., tabortdci., tabortwc., tabortwci. or treclaim. instruction, TEX-ASR<sub>31</sub> is set to 1, and, for *tabort*. and *treclaim*., a software defined failure code is copied from a register operand to TEXASR<sub>0:7</sub>. TEXASR<sub>Suspended</sub> indicates whether the transaction was in the Suspended state at the time that failure was recorded. The values of MSR<sub>HV</sub> and MSR<sub>PR</sub> at the time that failure is recorded are copied to TEXASR<sub>34</sub> and TEXASR<sub>35</sub>, respectively. If MSR<sub>PR</sub> is 0 at the time that failure is recorded, the value of MSR<sub>S</sub> is copied into TEXASR<sub>40</sub>. In some circumstances, the failure causing instruction address in TFIAR may not be exact. In such circumstances, TEX-ASR<sub>37</sub> is set to 0 indicating that the contents of TFIAR are not exact; otherwise TEXASR<sub>37</sub> is set to 1.

#### — Programming Note

The transaction level contained in  $\mathsf{TEXASR}_\mathsf{TL}$  should be interpreted by software as follows:

When in the Transactional or Suspended state, this field contains an unsigned integer representing the transaction level of the active transaction, with 1 indicating an outer transaction, and a number greater than 1 indicating a nested transaction. The nesting depth of the active transaction is TEXAS- $R_{TL}-1.$

When in the Non-transactional state,  $\text{TEXASR}_{\text{TL}}$  contains 0 if the last transaction committed successfully, otherwise it contains the transaction level at which the most recent transaction failed.

#### Programming Note

The Privilege and Secure bits in TEXASR represent the state of the machine at the point when failure is recorded. This information may be used by problem state software to determine whether an unexpected interaction with the operating system or with higher-privilege software (hypervisor or ultravisor) was responsible for transaction failure. (In problem state, *mftexasr* returns 0 for the Secure bit.) This information may be useful to operating systems, hypervisors, or ultravisors when restoring register state for failure handling after the transactional facility was reclaimed, to determine which level of software has retained the pre-transactional version of the checkpointed registers.

Note that any transfer of control to the hypervisor during a transaction initiated by a secure partition will cause the transaction to fail because the ultravisor must protect the checkpointed register values from the hypervisor, and therefore must execute *treclaim.* before passing control to the hypervisor. Thus if TEXASR reports that the failure was caused by *treclaim.* and occurred in ultravisor state, nothing is likely to be gained from additional analysis.

--- End text ------

# Section 5.4.3 Transaction Failure Instruction Address Register (TFIAR)

Fix for the addition of MSR[S] and explain why it needn't appear in the TFIAR.

----- Begin text ------

The Transaction Failure Instruction Address Register is a 64-bit SPR that is set to the exact effective address of the instruction causing the failure, when possible. Bits 62:63 contain the value that was in MSR<sub>HV</sub> || MSR<sub>PR</sub> when the failure was recorded.

| TFIA | Privi | ilege |

|------|-------|-------|

| 0    | 62    | 63    |

#### Figure 1. Transaction Failure Instruction Address Register (TFIAR)

In certain cases, the exact address may not be available, and therefore TFIAR will be an approximation. An approximate value will point to an instruction near the instruction that was executing at the time of the failure. TFIAR accuracy is recorded in an Exact bit residing in TEXASR<sub>37</sub>.

#### Programming Note

The purpose of the Privilege field in TFIAR is to prevent *mftfiar* executed in a given privilege state from returning an effective address that was recorded in a higher privilege state; see <xref to section 4.4.4 (mfspr)>. There is no need for mftfiar to prevent the hypervisor from returning an effective address that was recorded in ultravisor state because the ultravisor, running in Non-transactional state, can use TEXASR<sub>FS</sub> and TEXASR<sub>S</sub> HV PR to determine whether the most recent transaction failure occurred in ultravisor state and, if the most recent transaction failure did occur in ultravisor state, the ultravisor can set TFIAR to all 0s before passing control to the hypervisor. For this reason there is no need for TFIAR to contain the value that was in  $MSR_S$  when the failure was recorded.

----- End text ------

## Book 3S:

#### Section 1.2.1 Definitions and Notation

Add definitions of ultravisor and hypervisor interrupts. Delete trap interrupt.

exception

An error, unusual condition, or external signal, that may set a status bit and may or may not cause an interrupt, depending upon whether the corresponding interrupt is enabled.

----- Begin text -----

interrupt

The act of changing the machine state in response to an exception, as described in Chapter 6. "Interrupts" on page 1095.

- ultravisor interrupt

An interrupt that forces the thread into ultravisor state by explicitly setting MSR<sub>S HV PR</sub> to 0b110 (see <xref to section 3.2.1>).

- hypervisor interrupt

An interrupt that forces the thread into hypervisor state by explicitly setting MSR<sub>HV PR</sub> to 0b10 and is not an ultravisor interrupt.

- All interrupts explicitly set  $MSR_{PR}$  to 0.

----- End text -----

Update the definition of "must" as follows..

#### ----- Begin text -----

#### ∎ "must"

If software that runs in hypervisor state violates a rule that is stated using the word "must" (e.g., "this field must be set to 0"), and the rule pertains to the contents of a hypervisor resource, to executing an instruction that can be executed only in hypervisor state, or to accessing storage in real addressing mode, the results are undefined, and may include altering resources belonging to other partitions, causing the system to "hang", etc. The same is true for software that runs in ultravisor state and violates a "must" rule pertaining to an ultravisor resource or instruction.

----- End text -----

After the hardware bullet, add the following new bullet.

## ----- Begin text ---- ultravisor privileged

A term used to describe an instruction or facility that is available when and only when the thread is in ultravisor state.

----- End text -----

Update the definition of hypervisor privileged as follows to smooth over the addition of ultravisor.

Begin text ----- hypervisor privileged

A term used to describe an instruction or facility that is available when and only when the thread is in hypervisor state.

#### Programming Note —

Because ultravisor state is also a hypervisor state, hypervisor privileged instructions and facilities are also available when the thread is in ultravisor state. (The distinct privilege states in which a hypervisor privileged instruction or facility is available are: hypervisor non-ultravisor state, and ultravisor state.)

----- End text -----

Add the definition of privileged as follows for completeness.

## privileged

A term used to describe an instruction or facility that is available when and only when the thread is in privileged state.

#### Programming Note \_\_\_\_\_

Because hypervisor state is also a privileged state, privileged instructions and facilities are also available when the thread is in hypervisor state (and when the thread is in ultravisor state). (The distinct privilege states in which a privileged instruction or facility is available are: privileged non-hypervisor state, hypervisor non-ultravisor state, and ultravisor state.)

Section 1.4 Exceptions

After the second bullet, add the following as the third bullet.

----- End text ------

----- Begin text -----

an attempt to modify an ultravisor resource when the thread is in privileged but non-ultravisor state (see <crossref to new ch3>), or an attempt to execute an ultravisor-only instruction (e.g., *urfid*, *msgsndu*, *msgcIru*) when the thread is in privileged but non-ultravisor state

------ End text ------

RFC02487: Secure Memory Facility

# Section 2.2 Logical Partitioning Control Register (LPCR)

In the AIL definition, add the missing special case of scv. Add the ultravisor interrupts to the list that work as if AIL=0 and also interrupts taken by the ultravisor. Restructure the overrides to improve clarity.

----- Begin text -----

The overrides mentioned above are as follows. The list should be read from the top down; the first item matching a given situation applies.

- If the interrupt results in the thread being in ultravisor state, the interrupt is taken as if LPCR<sub>AIL</sub>=0.

- Machine Check, System Reset, and Hypervisor Maintenance interrupts are taken as if LPCR<sub>AIL</sub>=0.

- If the interrupt occurs when MSR<sub>IR</sub>=0 or MSR<sub>DR</sub>=0, the interrupt is taken as if LPCR<sub>AIL</sub>=0.

- If the interrupt causes a transition from MSR<sub>HV</sub>=0 to MSR<sub>HV</sub>=1 and HR=0, the interrupt is taken as if LPCR<sub>AIL</sub>=0.

----- End text -----

Extend the EVIRT definition to cover ultravisor-privileged resources and instructions.

----- Begin text -----

#### 42 Enhanced Virtualization (EVIRT)

Controls whether Enhanced Virtualization is enabled, as specified below.

- 0 Enhanced virtualization is disabled: attempts to execute hypervisor-privileged instructions or access hypervisor resources, or PTCR, DAWRO, DAWRXO, or CIABR when they are ultravisor resources, in privileged but non-hypervisor state cause a Privileged Instruction type Program interrupt; attempts to access undefined SPR numbers other than 0 for *mtspr* and 0, 4, 5, and 6 for *mfspr* in privileged state are treated as noops.

- 1 Enhanced virtualization is enabled: attempts to execute hypervisor-privileged instructions or access hypervisor resources, or PTCR, DAWR0, DAWRX0, or CIABR when they are ultravisor resources, in privileged but non-hypervisor state cause a Hypervisor Emulation Assistance interrupt; attempts to access undefined SPR numbers other than 0 for *mtspr* and 0, 4, 5, and 6 for *mfspr* in privileged state cause a Hypervisor Emulation Assistance interrupt.

----- End text -----

Change HR definition to be consistent with PATE[HR].

----- Begin text ------

#### 43 Host Radix (HR)

Indicates whether the hypervisor uses Radix Tree translation for the partition, as specified below.

- 0 hypervisor uses HPT translation for this partition.

- 1 hypervisor uses Radix Tree translation for this partition.

- **Programming Note** The hypervisor must program HR to match the Host Radix bit in the appropriate Partition Table Entry. If the values do not match when  $MSR_{HV} PR \neq 0b10$  or  $MSR_{IR DR} \neq 0b00$ , the results are undefined.

HR is duplicated in the LPCR because there are times such as immediately after a partition swap when it is difficult for hardware to quickly access the PATE.

------ End text ------

Section 2.5 Processor Compatibility Register (PCR)

Add urfid to [h]rfid as unaffected by the PCR with respect to its setting of the MSR.

------ Begin text ------

The PCR has no effect on the setting of the MSR and [H]SRR1 by interrupts (and of the Count Register by the System Call Vectored interrupt), and by the *rfscv*, *rfid*, *hrfid*, *urfid*, and *mtmsr[d]* instructions, except as specified elsewhere in this section.

----- End text -----

# Section 2.7 Sharing Hypervisor and Ultravisor Resources

Extend the section title. Add URMOR and SMFCTRL to the section. Also correct that PECE may differ by thread in LPCR.

----- Begin text -----

Certain additional hypervisor and ultravisor resources, and the PVR, may be shared among threads. Programs that modify these resources must be aware of this sharing, and must allow for the fact that changes to these resources may affect more than one thread. The following additional resources may be shared among threads.

- HRMOR (see Section 2.3)

- LPIDR (see Section 2.4)

- PCR (see Section 2.5)

- URMOR (see <crossref to ch3>)

- PVR (see Section 4.3.1)

- RPR (see Section 4.3.8)

- PTCR (see Section 5.7.6.1)

- AMOR (see Section 5.7.14.1)

- HMEER (see Section 6.2.10)

- Time Base (see Section 7.2)

- Virtual Time Base (see Section 7.3)

- Hypervisor Decrementer (see Section 7.5)

- certain implementation-specific registers or implementation-specific fields in architected registers

The set of resources that are shared is implementationdependent.

Threads that share any of the resources listed above, with the exception of the PTCR, the PVR, the URMOR, and the HRMOR, must be in the same partition.

For each field of the LPCR, except the AIL, ONL, LD,

PECE, HDICE, and MER fields, software must ensure that the contents of the field are identical among all threads that are in the same partition and are in a state such that the contents of the field could have side effects. (E.g., software must ensure that the contents of LPCR<sub>LPES</sub> are identical among all threads that are in the same partition and are not in hypervisor state.) For the HDICE field, software must ensure that the contents of the field are identical among all threads that share the Hypervisor Decrementer and are in a state such that the contents of the field could have side effects. There are no identity requirements for the other fields listed in the first sentence of this paragraph.

Software must ensure that the contents of UILE and  $SMFCTRL_E$  are identical among all threads in the system that have completed ultravisor initialization. The contents of the D and UDEE fields of SMFCTRL may differ among threads.

----- End text -----

# Section 2.10 Hypervisor Interrupt Little-Endian (HILE) Bit

Restate the circumstances for using HILE to allow for ultravisor state.

----- Begin text -----

The Hypervisor Interrupt Little-Endian (HILE) bit is a bit in an implementation-dependent register or similar mechanism. The contents of the HILE bit are copied into  $MSR_{LE}$  by interrupts that result in  $MSR_{S HV}$  being equal to 0b01 (see Section 6.5), to establish the Endian mode for the interrupt handler. The HILE bit is set, by an implementation-dependent method, only during system initialization. The contents of the HILE bit must be the same for all threads under the control of a given instance of the hypervisor; otherwise all results are undefined.

----- End text -----

Chapter 2+ Ultravisor and Secure Memory Facility (SMF)

Add the following chapter after Chapter 2, Logical Partitioning (LPAR) and Thread Control, to describe the ultravisor functionality and related support for the secure memory facility.

----- Begin text -----

## 3.1 Overview

The Secure Memory Facility (SMF) provides secure isolation of partitions from one another and from higher privilege system software. SMF functionality is implemented using a combination of hardware facilities and firmware that runs at a privilege level above the hypervisor. SMF targets a threat model in which the hypervisor can be compromised such that its inherent isolation capabilities can no longer be counted on. Maintaining the security of data is the sole objective of the ultravisor. It has no role in platform management and is not expected to deal with denial of service attacks. References elsewhere in the Books to "secure systems" apply more generally, and do not necessarily imply that the system uses SMF.

The SMF protection mechanism is based on the assignment of partitions to security domains. The hypervisor is in one security domain, along with all processes that run directly under the hypervisor and all partitions that do not take advantage of the SMF security capabilities. Each of the secure partitions is assigned to its own security domain so that its data and instructions can be protected from access by other security domains. A partition is identified as secure when MSR<sub>S</sub>=1. Each location in main storage has an associated Secure Memory property, mem<sub>SM</sub>. Memory with mem<sub>SM</sub>=1 may be referred to as "secure memory." Memory with mem<sub>SM</sub>=0 may be referred to as "ordinary memory." The granularity and method with which main storage is mapped for the Secure Memory property is implementation specific. The Secure Memory property is commonly cached in the TLB and in implementationspecific lookaside buffers. When secure data are to be shared with untrusted software, the standard synchronization associated with PTE updates is used to regulate access. For example, prior to sharing secure data, the PTEs used to access the data are marked invalid and the corresponding TLB entires invalidated by the ultravisor using the standard invalidation sequence. (See <crossref to pte update sequence desc>.) The data are then encrypted and made available in ordinary memory (either mem<sub>SM</sub> is turned off or the data are moved to ordinary memory). Finally the PTEs that will be used to access the data in ordinary memory are marked valid. (The last step may be done lazily.) Software running with MSR<sub>S</sub>=0 is prohibited from accessing secure memory. Software running with MSRs=1 may access both secure and ordinary memory.

#### – Programming Note –

The ultravisor will commonly use a no-execute protection setting to prevent a secure partition from executing instructions from any ordinary memory mapped into its address space.

SMF firmware runs in ultravisor state, a privilege level above that of the hypervisor. That firmware, along with the SMF hardware, is responsible for maintaining isolation of secure partitions from each other and from the hypervisor. This is accomplished by direct ultravisor management of the partition-scoped translation tables in secure memory for secure partitions. The ultravisor itself runs only in (ultravisor) real addressing mode. Security is the result of proper management of the partition-scoped translation together with the hardware enforcement of the access restriction for secure memory. With this hybrid approach, firmware has the ability to enable secure memory sharing between secure partitions and ordinary memory sharing between a given secure partition and the hypervisor, e.g. for system calls. The ultravisor can access any architecture resource or facility.

The hypervisor is expected to cooperate in the management of secure partitions by using ultravisor calls to dispatch them and to manage their storage allocations. To protect against programming errors and malicious hypervisor behavior, *mtmsr[d]*, *rfid*, *hrfid*, and *rfscv* preserve MSR<sub>S</sub> and hypervisor interrupts from secure partitions are always received in ultravisor state.

The purpose of intercepting hypervisor interrupts is to protect the state of the secure partition from the hypervisor. The ultravisor's interrupt handler provides a 'shim' that saves and clears the processing state, and then transfers control to the hypervisor to handle the exception condition itself. The ultravisor will restore the secure partition state when it services the ultravisor call to (re-) dispatch the secure partition. Note that the ultravisor's goal is merely to protect the security of data, and not to provide broader system management oversight.

#### Programming Note —

When the ultravisor intercepts an interrupt with a transaction active, it must save and restore the checkpointed registers (causing the transaction to fail).

# 3.2 Ultravisor Real Mode Offset Register (URMOR)

The layout of the Ultravisor Real Mode Offset Register (URMOR) is shown in Figure 2 below.

| // | URMO |    |

|----|------|----|

| 0  | 4    | 63 |

Bit(s) Name Description 4:63 URMO Real Mode Offset

#### Figure 2. Ultravisor Real Mode Offset Register

All other fields are reserved.

The supported URMO values are the non-negative multiples of  $2^{r}$ , where r is the same implementationdependent value that constrains the HRMO field of the HRMOR.

The contents of the URMOR affect how some storage accesses are performed as described in <crossref to Real and Virtual Real Addressing modes section> and <crossref to Address Ranges Having Defined Uses section>.

## 3.3 Ultravisor Interrupt Little-Endian (UILE) Bit

The Ultravisor Interrupt Little-Endian (UILE) bit is a bit in an implementation-dependent register or similar mechanism. The contents of the UILE bit are copied into  ${\rm MSR}_{\rm LE}$  by interrupts that result in  ${\rm MSR}_{\rm S\,HV}$  being equal to 0b11 (see Section 6.5), to establish the Endian mode for the interrupt handler. The UILE bit is set, by an implementation-dependent method, only during system initialization.

The contents of the UILE bit must be the same for all threads in the system; otherwise all results are undefined.

## 3.4 Secure Memory Facility Control Register (SMFCTRL)

The Secure Memory Facility Control Register (SMFC-TRL) is shown in Figure 3 below.

| Е | D | UDEE |   | /// | ??    |

|---|---|------|---|-----|-------|

| 0 | 1 | 2    | 3 |     | 62 63 |

Figure 3. Secure Memory Facility Control Register (SMFCTRL)

Bit Description

0 SMF Enable (E)

- 0 SMF functionality including secure memory checking is disabled.

- 1 SMF functionality including secure memory checking is enabled.

When  $SMFCTRL_E=1$ , writing the PTCR is ultravisor privileged.

#### Debug enable (D)

1

2

- 0 Ultravisor debug mode is disabled.

- 1 Ultravisor debug mode is enabled.

In ultravisor debug mode, CIABR, DAWRn, and DAWRXn are ultravisor privileged. See <crossref to ch.8> for a description of how instruction and data address tracing work in ultravisor debug mode.

Ultravisor Doorbell Exit Enable (UDEE)

- 0 When the *stop* instruction is executed with PSSCR<sub>EC</sub>=1, Directed Ultravisor Doorbell exceptions are not enabled to cause exit from power-saving mode

- 1 When the **stop** instruction is executed with PSSCR<sub>EC</sub>=1, Directed Ultravisor Doorbell exceptions are enabled to cause exit from power-saving mode.

- 3:61 Reserved

- 62:63 Implementation-specific use

$\begin{array}{l} {\sf SMFCTRL}_E \text{ must be set to 1 prior to exiting ultravisor} \\ {\sf state if the system will use the SMF facilities. (When ${\sf SMFCTRL}_E=0$ and ${\sf MSR}_S=0$, there is no way to achieve ${\sf MSR}_S=1$ without a reboot.) \\ \end{array}$

#### Programming Note

The two useful runtime states with respect to SMF operation are (1)  $MSR_S=0$  and  $SMFCTRL_E=0$  (SMF permanently disabled) and (2)  $SMFCTRL_E=1$  (SMF enabled). Very limited verification may be performed on the state with  $MSR_S=1$  and  $SMFC-TRL_E=0$  and around state changes of  $SMFC-TRL_E=0$  and around state changes of  $SMFC-TRL_E$ . Therefore, software should change the value of  $SMFCTRL_E$  at most once, making the change prior to the first dispatch of a partition, and spending as little time as possible in the state with  $MSR_S=1$  and  $SMFCTRL_E=0$ .

If SMFCTRL<sub>E</sub>=0, SMFCTRL<sub>D</sub> and SMFCTRL<sub>UDEE</sub> must be set to zero. References to SMFCTRL<sub>D</sub>=1 or SMFCTRL<sub>UDEE</sub>=1 elsewhere in the architecture assume SMFCTRL<sub>E</sub>=1 unless otherwise stated or obvious from context.

## 3.4.1 Enabling SMF and Secure Memory Enforcement

The SMFCTRL<sub>E</sub> bit enables SMF functionality. When SMFCTRL<sub>E</sub>=1, certain facilities are ultravisor resources

instead of hypervisor resources and secure memory checking is enabled.

Independent of the basic feature enablement above, SMF has state transition rules that facilitate the protection of security domains. (While these rules are nominally independent of the value of SMFCTRL<sub>E</sub>, some transitions cannot happen when SMFCTRL<sub>E</sub>=0. Specifically, ultravisor interrupts cannot occur when SMFC-TRL<sub>F</sub>=0.)

- All interrupts that are not ultravisor interrupts preserve MSR<sub>S</sub>. (Ultravisor interrupts necessarily set MSR<sub>S</sub> to 1.)

- mtmsr[d], rfid, hrfid, and rfscv are not permitted to change MSR<sub>S</sub>

Table 1 summarizes the effect of the SMFCTRL\_E bit and the  $\text{MSR}_{\text{S HV PR}}$  bits on various facilities.

| facility                                                                                 | MSR <sub>S HV PR</sub>  | SMFCTRLE | LPCR <sub>EVIRT</sub> | behavior                                              |

|------------------------------------------------------------------------------------------|-------------------------|----------|-----------------------|-------------------------------------------------------|

| <i>mtspr</i> or <i>mfspr</i> specifying                                                  | 110                     | dc       | dc                    | execution allowed                                     |

| URMOR, USRR0, USRR1,<br>USPRG0, USPRG1, or<br>SMFCTRL;<br><i>urfid, msgsndu, msgcIru</i> | all xxx<br>except 110** | dc       | dc                    | Privileged Instruction type Program inter rupt to xx0 |

| mtspr specifying PTCR                                                                    | 110                     | dc       | dc                    | execution allowed                                     |

|                                                                                          | 010                     | 0        | dc                    | execution allowed                                     |

|                                                                                          |                         | 1        | dc                    | HEAI to 010                                           |

|                                                                                          | x00                     | dc       | 0                     | Privileged Instruction type Program inter rupt to x00 |

|                                                                                          |                         |          | 1                     | HEAI to x10                                           |

|                                                                                          | xx1**                   | dc       | dc                    | Privileged Instruction type Program inter rupt to xx0 |

| <i>mtspr</i> or <i>mfspr</i> specifying                                                  | 110                     | 1        | dc                    | execution allowed                                     |

| DAWR0, DAWRX0 or CIABR                                                                   | 010                     | 1        | dc                    | HEAI to 010                                           |

| when SMFCTRL <sub>D</sub> =1                                                             | x00                     | 1        | 0                     | Privileged Instruction type Program inter rupt to x00 |

|                                                                                          |                         |          | 1                     | HEAI to x10                                           |

|                                                                                          | xx1**                   | 1        | dc                    | Privileged Instruction type Program inter rupt to xx0 |

| sc 2 instruction                                                                         | dc**                    | 0        | dc                    | hypervisor call, but with SRR1 showing LEV=2          |

|                                                                                          | dc**                    | 1        | dc                    | ultravisor call                                       |

| mem <sub>SM</sub> evaluation and                                                         | dc**                    | 0        | dc                    | disabled                                              |

| match                                                                                    | dc**                    | 1        | dc                    | enabled*                                              |

dc = don't care

\*\* The encoding  $MSR_{S HV PR}$ =0b111 is reserved and must not be used.

Table 1: Ultravisor Resource Behavior

#### Programming Note

I

Access to memory by mechanisms outside the core must also enforce secure memory access restrictions. Facilities that translate addresses or otherwise use real addresses to access memory must check mem<sub>SM</sub> against PATE<sub>S</sub> for the partition on behalf of which they access memory.

Such mechanisms will require a means to evaluate  $mem_{SM}$  and a proxy for  $SMFCTRL_E$  to provide the same enablement function for secure memory access enforcement as in the core.

In addition or as an alternative, TCE tables may be managed by the ultravisor and used to identify regions of memory that I/O devices may access.

----- End text ------

#### Section 3.2.1 Machine State Register

Add the S bit and references to **urfid**, as needed. Also specify that SF must be set to 1 in ultravisor state.

------ Begin text ------

The Machine State Register (MSR) is a 64-bit register. This register defines the state of the thread. On interrupt, the MSR bits are altered in accordance with Figure 55 on page 1010. The MSR can also be modified by the *mtmsr[d]*, *rfscv*, *rfid*, *hrfid* and *urfid* instructions. It can be read by the *mfmsr* instruction.

MSR

#### Figure 4. Machine State Register

Below are shown the bit definitions for the Machine State Register.

- Bit Description

- 0 Sixty-Four-Bit Mode (SF)

- 0 The thread is in 32-bit mode.

- 1 The thread is in 64-bit mode.

Software must ensure that SF=1 whenever the thread is in ultravisor state.

1:2 Reserved

#### 3 Hypervisor State (HV)

- 0 The thread is not in hypervisor state.

- If MSR<sub>PR</sub>=0, the thread is in hypervisor state; otherwise the thread is not in hypervisor state.

Programming Note

The privilege state of the thread is determined by  $\text{MSR}_{\text{S}},$   $\text{MSR}_{\text{HV}},$  and  $\text{MSR}_{\text{PR}},$  as follows.

S HV PR 0 x 1 problem 1 0 1 problem x x 0 privilege

1

63

xx0privilegedx10hypervisor110ultravisor

1 1 reserved

Hypervisor state is also a privileged state ( $MSR_{PR} = 0$ ). All references to "privileged state" in the Books include hypervisor state unless otherwise stated or obvious from context. Ultravisor state is also a hypervisor state ( $MSR_{HV PR} = 0b10$ ). All references to "hypervisor state" in the Books include ultravisor state unless otherwise stated or obvious from context.

MSR<sub>HV</sub> can be set to 1 only by the *System Call* instruction and some interrupts. It can be set to 0 only by *rfid*, *hrfid* and *urfid*.

It is possible to run an operating system in an environment that lacks a hypervisor, by always having  $MSR_{HV} = 1$  and using  $MSR_{HV PR} = 0b10$  for the operating system (effectively, the OS runs in hypervisor state) and  $MSR_{HV PR} = 0b11$  for applications. In this use,  $MSR_S$  would be 0, and the environment would also lack an ultravisor.

#### Reserved

4

5

Software must ensure that this bit contains 0; otherwise the results of executing all instructions are boundedly undefined.

#### Programming Note

This bit is initialized to 0 by hardware at system bringup. The handling of this bit by interrupts and by the *rfid*, *hrfid*, *urfid*, and *rfscv* instructions is such that, unless software deliberately sets the bit to 1, the bit will continue to contain 0.

6:28 Reserved

29:30 Transaction State (TS)

- 00 Non-transactional

- 01 Suspended

- 10 Transactional

- 11 Reserved

Changes to MSR[TS] that are caused by Transactional Memory instructions, and by invocation of the transaction's failure handler, take effect immediately (even though these instructions and events are not context synchronizing).

#### Transactional Memory Available (TM) 31

- The thread cannot execute any Transac-0 tional Memory instructions or access any Transactional Memory registers.

- The thread can execute Transactional 1 Memory instructions and access Transactional Memory registers unless the Transactional Memory facility has been made unavailable by some other register.

#### Programming Note

To access Transactional Memory registers and execute Transactional Memory instructions, it must also be true that HFSCR<sub>TM</sub>=1 or the thread is in hypervisor state. See Section 6.2.12 on page 1099 for more information.

#### 32:37 Reserved

- 38 Vector Available (VEC)

- The thread cannot execute any vector 0 instructions, including vector loads, stores, and moves.

- 1 The thread can execute vector instructions unless they have been made unavailable by some other register.

- 39 Reserved

#### 40 VSX Available (VSX)

- The thread cannot execute any VSX instructions, including VSX loads, stores, and moves.

- 1 The thread can execute VSX instructions unless they have been made unavailable by some other register.

#### Programming Note –

An application binary interface defined to support Vector-Scalar operations should also specify a requirement that MSR<sub>FP</sub> and MSR<sub>VEC</sub> be set to 1 whenever MSR<sub>VSX</sub> is set to 1.

- 41 Secure (S)

- 0 The thread is not in Secure state. It may not access Secure memory. The thread is not in ultravisor state.

- 1 The thread is in Secure state. lf MSR<sub>HV</sub>=1 and MSR<sub>PR</sub>=0, the thread is in ultravisor state; otherwise the value does not affect privilege. The state with

MSR<sub>HV</sub>=1 and MSR<sub>PR</sub>=1 is reserved. Software must not set MSR<sub>S HV PR</sub> = 0b111. References elsewhere in this document to MSR<sub>HV PR</sub>=0b11 assume MSR<sub>S</sub>=0 unless otherwise stated or obvious from context.

#### Programming Note —

MSR<sub>S</sub> can be set to 1 only by the System Call instruction and some interrupts. It can be set to 0 only by urfid.

Any instruction or event that causes MSR<sub>S HV PR</sub> to be set to 0b110 also causes MSR<sub>IR</sub> and MSR<sub>DR</sub> to be set to 0.

#### 42:47 Reserved

#### ...48 External Interrupt Enable (EE)

- 0 External, Decrementer, Performance Monitor, and Privileged Doorbell interrupts are disabled.

- External, Decrementer, Performance 1 Monitor, and Privileged Doorbell interrupts are enabled.

This bit also affects whether Hypervisor Decrementer, Hypervisor Maintenance, Directed Hypervisor Doorbell, and Directed Ultravisor Doorbell interrupts are enabled; see Section 6.5.12 on page 1122, Section 6.5.19 on page 1130, Section 6.5.20 on page 1131, and <crossref to ultravisor doorbell int>.

#### 49 Problem State (PR)

- The thread is in privileged state. 0

- If MSR<sub>S HV</sub>  $\neq$  0b11, the thread is in prob-1 lem state.

#### Programming Note –

Any instruction that sets MSR<sub>PR</sub> to 1 also sets MSR<sub>EE</sub>, MSR<sub>IR</sub>, and MSR<sub>DR</sub> to 1.

The state with MSR<sub>S HV PR</sub>=0b111 is reserved.

... 51

#### Machine Check Interrupt Enable (ME)

- 0 Machine Check interrupts are disabled.

- Machine Check interrupts are enabled. 1

This bit is a hypervisor resource; see Chapter 2., "Logical Partitioning (LPAR) and Thread Control", on page 879.

Programming Note –

The only instructions that can alter MSR<sub>MF</sub> are *rfid*, *hrfid* and *urfid*.

#### 52 Floating-Point Exception Mode 0 (FE0) [Category: Floating-Point]

See below.

#### 53:54 Trace Enable (TE)

- 00 Trace Disabled: The thread executes instructions normally.

- 01 Branch Trace: The thread generates a Branch type Trace interrupt after completing the execution of a branch instruction, whether or not the branch is taken.

- 10 Single Step Trace: The thread generates a Single-Step type Trace interrupt after successfully completing the execution of the next instruction, unless that instruction is a urfid, hrfid, rfid, rfscv, or a Power-Saving Mode instruction, all of which are never traced. Successful completion means that the instruction caused no other interrupt and, if the processor is in the Transactional state, is not one of the instructions that is forbidden in Transactional state (e.g., dcbf; see Section 4.3.1 of Book II).

- 11 Reserved

Branch tracing need not be supported. If the function is not implemented, the 0b01 bit encoding is treated as reserved.

#### 58 Instruction Relocate (IR)

. . .

...

- 0 Instruction address translation is disabled. 1

- Instruction address translation is enabled.

Programming Note -

See the Programming Note in the definition of MSR<sub>S</sub> and in the definition of MSR<sub>PR</sub>.

#### 59 Data Relocate (DR)

- Data address translation is disabled. 0 Effective Address Overflow (EAO) (see Book I) does not occur.

- Data address translation is enabled. EAO 1 causes a Data Storage interrupt.

#### Programming Note -

See the Programming Note in the definition of MSR<sub>S</sub> and in the definition of MSR<sub>PR</sub>.

#### 63 Little-Endian Mode (LE)

- 0 The thread is in Big-Endian mode.

- The thread is in Little-Endian mode. 1

### Programming Note -

The only instructions that can alter MSR<sub>IF</sub> are *rfid*, *hrfid, urfid*, and rfscv.

The initial state of the MSR should be as follows:

| Bit    | Name | Value |

|--------|------|-------|

| <br>41 | S    | 1     |

----- End text ------

#### Section 3.2.2 State Transitions Associated with the Transactional Memory Facility

Add urfid to each place in the section where the other \*rfid's are listed. The same TM state change restrictions should apply to urfid. (USRR1 will also need to be added to the last one before the e-note.) Special related explanation is added to the last p-note in the section as follows.

------ Begin text -----

#### Programming Note

I

For *rfscv, rfid*, *hrfid*, *urfid* and *mtmsrd*, the attempted transition from S0 to N0 is suppressed in order that interrupt handlers that are "unaware" of transactional memory, and load an MSR value that has not been updated to take account of transactional memory, will continue to work correctly. (If the interrupt occurs when a transaction is running or suspended, the interrupt will set MSR[TS || TM] to S0. If the interrupt handler attempts to load an MSR value that has not been updated to take account of transactional memory, that MSR value will have TS || TM = N0. It is desirable that the interrupt handler remain in state S0, so that it can return normally to the interrupted transaction.)

The problem solved by suppressing this transition does not apply to *rfebb*, so for *rfebb* an attempt to transition from S0 to N0 is not suppressed, and instead causes a TM Bad Thing type Program interrupt.

(The problem solved by suppressing this transition does not apply to *urfid* either, since *urfid* was added to the architecture after Transactional Memorv was added. The transition is suppressed for urfid because urfid is very similar to [h]rfid.)

------ End text -----

# Section 3.2.3 Processor Stop Status and Control Register (PSSCR)

Change "secure environments" to "secure systems" in the second p-note for consistency with other such references.

----- Begin text -----

– Programming Note –

Before dispatching an OS, the hypervisor may initialize this field to 1 in order to prevent the OS from reading the Power-Saving Level Status (PLS) field. This may be necessary in secure systems since an OS may be capable of detecting the presence of another OS on the same processor by observing the state of the PLS field after exiting power-saving mode.

Add behavior for loss of UDEE to the end of the ESL description just before the notes.

----- End text ------

----- Begin text -----

For power-saving levels that allow loss of SMFCTRL, implementations must provide the means to exit power-saving mode upon the occurrence of a Directed Ultravisor Doorbell exception if SMFCTRL<sub>UDEE</sub> was set to 1 when *stop* was executed. For this case, the implementation is also allowed to exit on the occurrence of a Directed Ultravisor Doorbell exception if

SMFCTRL<sub>UDEE</sub> was set to 0 when stop was executed.

------ End text ------

Add UDEE and ultravisor doorbell to the wakeup description for EC=1.

------ Begin text -----

1 If SMFCTRL<sub>UDEE</sub> was set to 1 when *stop* was executed and SMFCTRL<sub>UDEE</sub> was not lost, hardware will exit power-saving mode when a Directed Ultravisor Doorbell exception occurs. If LPCR<sub>PECE</sub> is not lost, hardware will exit power-saving mode when a System Reset exception or one of the events specified in LPCR<sub>PECE</sub> occurs. If the event is a Machine Check exception, then a Machine Check interrupt occurs; otherwise a System Reset interrupt occurs, and the contents of SRR1 indicate the event that caused exit from power-saving mode.

----- End text -----

#### Section 3.3.1 System Linkage Instructions

Adjust the LEV field description in the description of the sc instruction as follows:

----- Begin text -----

Then a System Call interrupt is generated. The interrupt causes the MSR to be set as described in Section 6.5, "Interrupt Definitions" on page 1009. The setting of the MSR is affected by the contents of the LEV field. LEV values greater than 2 are reserved. Bits 0:4 of the LEV field (instruction bits 20:24) are treated as a reserved field.

The interrupt causes the next instruction to be fetched from effective address 0x0000 0000 0000 0C00.

This instruction is context synchronizing.

SRR0 SRR1 MSR

— Programming Note ——

If LEV=1, the hypervisor is invoked.

If LEV=2 and SMFCTRL<sub>E</sub> = 1, the ultravisor is invoked.

If LEV=2 and SMFCTRL<sub>E</sub> = 0, the hypervisor is invoked. However, such invocation should be considered a programming error.

Executing this instruction with LEV=1 or LEV=2 is the only way that executing an instruction can cause a transition from non-hypervisor state to hypervisor state on the thread that executed the instruction. Executing this instruction with LEV=2 when SMFCTRL<sub>E</sub>=1 is the only way that executing an instruction can cause a transition from non-ultravisor state to ultravisor state on the thread that executed the instruction.

In correct use, this instruction is used to "call up" one privilege level (application program calls operating system, operating system calls hypervisor, hypervisor calls ultravisor). However, it is possible for a program to call up more than one level (e.g., for an application program to call the hypervisor). An attempt to call up more than one level should be considered a programming error.

----- End text -----

In the description of rfscv, don't allow S (41) to be changed. Also prevent translation from being enabled in ultravisor state. Also eliminate MSR[LE] (bit 63). Add USRR0 to the [H]SRR0s for an enabled pending exception. Make corresponding changes (and fixes) to the p-note following the verbal description.

```

& ¬ (MSR<sub>41</sub> & MSR<sub>3</sub> & (¬CTR<sub>49</sub>))

MSR<sub>0:2</sub> 4:28 32 37:40 49:50 52:57 60:63 ← CTR<sub>0:2</sub> 4:28 32 37:40 49:50 52:57

60:63

NIA ←<sub>iea</sub> LR<sub>0:61</sub> || 0b00

```

If bits 29 through 31 of the MSR are not equal to 0b010 or bits 29 through 31 of the Count Register are not equal to 0b000, then the value of bits 29 through 31 of the Count Register is placed into bits 29 through 31 of the MSR. The result of ORing bits 48 and 49 of the Count Register is placed into MSR<sub>48</sub>. The result of ANDing bit 41 of the MSR with bit 3 of the MSR and with the complement of bit 49 of the Count Register is complemented and then ANDed with the result of ORing bits 58 and 49 of the Count Register and placed into MSR<sub>58</sub>. The result of ANDing bit 41 of the MSR with bit 3 of the MSR and with the complement of bit 49 of the Count Register is complemented and then ANDed with the result of ORing bits 59 and 49 of the Count Register and placed into MSR<sub>50</sub>. Bits 0:2, 4:28, 32, 37:40, 49:50, 52:57, and 60:63 of the Count Register are placed into the corresponding bits of the MSR.

If the instruction attempts to cause an illegal transaction state transition (see Table 3, "Transaction state transitions that can be requested by rfebb, rfid, rfscv, hrfid, and mtmsrd.," on page 984), or when TM is disabled by the PCR, a transition to Problem state with an active transaction, a TM Bad Thing type Program interrupt is generated (unless a higher-priority exception is pending). If this interrupt is generated, the value placed into SRR0 by the interrupt processing mechanism (see Section 6.4.3) is the address of the *rfid* instruction. Otherwise, if the new MSR value does not enable any pending exceptions, then the next instruction is fetched, under control of the new MSR value, from the address LR<sub>0:61</sub> || 0b00 (when SF=1 in the new MSR value) or <sup>32</sup>0 || LR<sub>32:61</sub> || 0b00 (when SF=0 in the new MSR value). If the new MSR value enables one or more pending exceptions, the interrupt associated with the highest priority pending exception is generated; in this case the value placed into SRR0, HSRR0, or USRR0 by the interrupt processing mechanism (see Section 6.4.3) is the address of the instruction that would have been executed next had the interrupt not occurred.

This instruction is privileged and context synchronizing.

#### Special Registers Altered: MSR

- Programming Note

If this instruction sets  $MSR_{PR}$  to 1, it also sets  $MSR_{EE}$ ,  $MSR_{IR}$ , and  $MSR_{DR}$  to 1. If this instruction results in  $MSR_{S HV PR}$  being equal to 0b110, it also sets  $MSR_{IR}$  and  $MSR_{DR}$  to 0.

This instruction does not alter  $\text{MSR}_{\text{HV}}, \, \text{MSR}_{\text{S}}, \,$  or  $\text{MSR}_{\text{ME}}.$

----- End text ------

In the description of rfid, don't allow S (41) to be changed. Also don't allow translation to be enabled in ultravisor state.

| Begin text                                                                                                                                                                                                                                                                                               |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Degin text                                                                                                                                                                                                                                                                                               |

| $\begin{array}{l} \text{MSR}_{51} \leftarrow (\text{MSR}_3 \& \text{SRR1}_{51}) &   & ((\neg \text{MSR}_3) \& \text{MSR}_{51}) \\ \text{MSR}_3 \leftarrow \text{MSR}_3 \& \text{SRR1}_3 \\ \text{if } (\text{MSR}_{29:31} \neg = 0b010 &   & \text{SRR1}_{29:31} \neg = 0b000) \text{ then} \end{array}$ |

| $MSR_{29:31} \leftarrow SRR1_{29:31}$ $MSR_{48} \leftarrow SRR1_{48}   SRR1_{49}$                                                                                                                                                                                                                        |

| $MSR_{58} \leftarrow (SRR1_{58}   SRR1_{49})$                                                                                                                                                                                                                                                            |

| $\& \neg (MSR_{41} \& MSR_3 \& (\neg SRR1_{49}))$                                                                                                                                                                                                                                                        |

| $MSR_{59} \leftarrow (SRR1_{59}   SRR1_{49})$                                                                                                                                                                                                                                                            |

| $\& \neg (MSR_{41} \& MSR_3 \& (\neg SRR1_{49}))$                                                                                                                                                                                                                                                        |

| <sup>MSR</sup> 0:2 4:28 32 37:40 49:50 52:57 60:63 <sup>←</sup> SRR10:2 4:28 32 37:40 49:50 52:57                                                                                                                                                                                                        |

| 60:63<br>NIA ← <sub>iea</sub> SRR0 <sub>0:61</sub>    0b00                                                                                                                                                                                                                                               |

If MSR<sub>3</sub>=1 then bits 3 and 51 of SRR1 are placed into the corresponding bits of the MSR. If bits 29 through 31 of the MSR are not equal to 0b010 or bits 29 through 31 of SRR1 are not equal to 0b000, then the value of bits 29 through 31 of SRR1 is placed into bits 29 through 31 of the MSR. The result of ORing bits 48 and 49 of SRR1 is placed into MSR<sub>48</sub>. The result of ANDing bit 41 of the MSR with bit 3 of the MSR and with the complement of bit 49 of SRR1 is complemented and then ANDed with the result of ORing bits 58 and 49 of SRR1 and placed into MSR<sub>58</sub>. The result of ANDing bit 41 of the MSR with bit 3 of the MSR and with the complement of bit 49 of SRR1 is complemented and then ANDed with the result of ORing bits 59 and 49 of SRR1 and placed into MSR<sub>59</sub>. Bits 0:2, 4:28, 32, 37:40, 49:50, 52:57, and 60:63 of SRR1 are placed into the corresponding bits of the MSR.

----- Begin text ------

... If the new MSR value enables one or more pending exceptions, the interrupt associated with the highest priority pending exception is generated; in this case the value placed into SRR0, HSRR0, or USRR0 by the interrupt processing mechanism (see Section 6.4.3) is the address of the instruction that would have been executed next had the interrupt not occurred.

This instruction is privileged and context synchronizing.

## **Special Registers Altered:**

MSR

#### — Programming Note —

If this instruction sets  $MSR_{PR}$  to 1, it also sets  $MSR_{EE}$ ,  $MSR_{IR}$ , and  $MSR_{DR}$  to 1. If this instruction results in  $MSR_{S HV PR}$  being equal to 0b110, it also sets  $MSR_{IR}$  and  $MSR_{DR}$  to 0.

----- End text ------

In the description of hrfid, don't allow S (41) to be changed. Also don't allow translation to be enabled in ultravisor state.

----- Begin text ------

if (MSR<sub>29:31</sub> ¬= 0b010 | HSRR1<sub>29:31</sub> ¬= 0b000) then MSR<sub>29:31</sub> ← HSRR1<sub>29:31</sub> MSR<sub>48</sub> ← HSRR1<sub>48</sub> | HSRR1<sub>49</sub> MSR<sub>58</sub> ← (HSRR1<sub>58</sub> | HSRR1<sub>49</sub>) & ¬(MSR<sub>41</sub> & HSRR1<sub>3</sub> & (¬HSRR1<sub>49</sub>)) MSR<sub>59</sub> ← (HSRR1<sub>59</sub> | HSRR1<sub>49</sub>) & ¬(MSR<sub>41</sub> & HSRR1<sub>3</sub> & (¬HSRR1<sub>49</sub>)) MSR<sub>0:28</sub> 32 37:40 49:57 60:63 ← HSRR1<sub>0:28</sub> 32 37:40 49:57 60:63 NIA ← iea HSRR0<sub>0:61</sub> || 0b00

If bits 29 through 31 of the MSR are not equal to 0b010 or bits 29 through 31 of HSRR1 are not equal to 0b000, then the value of bits 29 through 31 of HSRR1 is placed into bits 29 through 31 of the MSR. The result of ORing bits 48 and 49 of HSRR1 is placed into  $MSR_{48}$ . The result of ANDing bit 41 of the MSR with bit 3 of HSRR1 and with the complement of bit 49 of HSRR1 is complemented and then ANDed with the result of ORing bits 58 and 49 of HSRR1 and placed into  $MSR_{58}$ . The result of ANDing bit 41 of the MSR with bit 3 of HSRR1 and with the complement of bit 49 of HSRR1 is complemented and then ANDed with the result of ORing bits 58 and 49 of HSRR1 and placed into  $MSR_{58}$ . The result of ANDing bit 41 of the MSR with bit 3 of HSRR1 and with the complement of bit 49 of HSRR1 is complemented and then ANDed with the result of ORing bits 59 and 49 of HSRR1 and placed into  $MSR_{59}$ . Bits 0:28, 32, 37:40, 49:57, and 60:63 of HSRR1 are placed into the corresponding bits of the MSR.

If the instruction attempts to cause an illegal transaction state transition (see Table 3, "Transaction state transitions that can be requested by rfebb, rfid, rfscv, hrfid, and mtmsrd.," on page 984), or when TM is disabled by the PCR, a transition to Problem state with an active transaction, a TM Bad Thing type Program interrupt is generated (unless a higher-priority exception is pending). If this interrupt is generated, the value placed into SRR0 by the interrupt processing mechanism (see

Section 6.4.3) is the address of the *hrfid* instruction. Otherwise, if the new MSR value does not enable any pending exceptions, then the next instruction is fetched, under control of the new MSR value, from the address HSRR0<sub>0:61</sub> || 0b00 (when SF=1 in the new MSR value) or <sup>32</sup>0 || HSRR0<sub>32:61</sub> || 0b00 (when SF=0 in the new MSR value). If the new MSR value enables one or more pending exceptions, the interrupt associated with the highest priority pending exception is generated; in this case the value placed into SRR0, HSRR0, or USRR0 by the interrupt processing mechanism (see Section 6.4.3) is the address of the instruction that would have been executed next had the interrupt not occurred.

----- End text -----

----- Begin text -----

After the description of hrfid add urfid:

----- Begin text -----

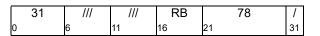

## Ultravisor Return From Interrupt Doubleword XL-form

urfid

| 19 |   |    |    | 306 | /  |

|----|---|----|----|-----|----|

| 0  | 6 | 11 | 16 | 21  | 31 |

if (MSR<sub>29:31</sub> ¬= 0b010 | USRR1<sub>29:31</sub> ¬= 0b000) then MSR<sub>29:31</sub> ← USRR1<sub>29:31</sub> MSR<sub>48</sub> ← USRR1<sub>48</sub> | USRR1<sub>49</sub> MSR<sub>58</sub> ← (USRR1<sub>58</sub> | USRR1<sub>49</sub>) & ¬(USRR1<sub>41</sub> & USRR1<sub>3</sub> & (¬USRR1<sub>49</sub>)) MSR<sub>59</sub> ← (USRR1<sub>59</sub> | USRR1<sub>3</sub>) & ¬(USRR1<sub>41</sub> & USRR1<sub>3</sub> & (¬USRR1<sub>49</sub>)) MSR<sub>0:28 32 37:41 49:57 60:63</sub> ← USRR1<sub>0:28 32 37:41 49:57 60:63</sub> NIA ← iea USRR0<sub>0:61</sub> || 0b00

If bits 29 through 31 of the MSR are not equal to 0b010 or bits 29 through 31 of USRR1 are not equal to 0b000, then the value of bits 29 through 31 of USRR1 is placed into bits 29 through 31 of the MSR. The result of ORing bits 48 and 49 of USRR1 is placed into MSR<sub>48</sub>. The result of ANDing bit 41 of USRR1 with bit 3 of USRR1 and with the complement of bit 49 of USRR1 is complemented and then ANDed with the result of ORing bits 58 and 49 of USRR1 and placed into MSR<sub>58</sub>. The result of ANDing bit 41 of USRR1 with bit 3 of USRR1 and with the complement of bit 49 of USRR1 is complemented and then ANDed with the result of ORing bits 59 and 49 of USRR1 and placed into MSR<sub>59</sub>. Bits 0:28, 32, 37:41, 49:57, and 60:63 of USRR1 are placed into the corresponding bits of the MSR.

If the instruction attempts to cause an illegal transaction state transition or, when TM is made unavailable in problem state by the PCR, attempts to cause a transition to problem state and also a transaction state transition that Table 3 on page 987 shows as legal and as resulting in the thread being in Transactional or Suspended state, a TM Bad Thing type Program interrupt is generated (unless a higher-priority exception is pending). If this interrupt is generated, the value placed into SRR0 by the interrupt processing mechanism (see Section 6.4.3) is the address of the **urfid** instruction. Otherwise, if the new MSR value does not enable any pending exceptions, then the next instruction is fetched, under control of the new MSR value, from the address USRR0<sub>0:61</sub> || 0b00 (when SF=1 in the new MSR value) or <sup>32</sup>0 || USRR0<sub>32:61</sub> || 0b00 (when SF=0 in the new MSR value). If the new MSR value enables one or more pending exceptions, the interrupt associated with the highest priority pending exception is generated; in this case the value placed into SRR0, HSRR0, or USRR0 by the interrupt processing mechanism (see Section 6.4.3) is the address of the instruction that would have been executed next had the interrupt not occurred.

This instruction is ultravisor privileged and context synchronizing.

Special Registers Altered: MSR

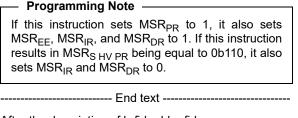

#### Programming Note -

If this instruction sets  $\rm MSR_{PR}$  to 1, it also sets  $\rm MSR_{EE}, \, MSR_{IR},$  and  $\rm MSR_{DR}$  to 1. If this instruction sets  $\rm MSR_{S}$   $_{\rm HV}$   $_{PR}$  to 0b110, it also sets  $\rm MSR_{IR}$  and  $\rm MSR_{DR}$  to 0.

----- End text -----

#### Section 3.3.2 Power-Saving Mode

Add the ultravisor equivalent in the last bullet.

#### ----- Begin text -----

*Power-Saving Mode* is a mode in which the thread does not execute instructions and may consume less power than it would if it were not in power-saving mode. The thread can be put in power-saving mode by executing the *stop* instruction.

There are 16 levels of power savings, designated as levels 0-15. For each power-saving level, the power consumed may be less than or equal to the power consumed in the next-lower level, and the time required for the thread to exit power-saving mode and resume execution may be greater than or equal that of the nextlower level.

When the thread is in power-saving mode, some resource state may be lost. The state that may be lost while in each power-saving level is implementation dependent, with the following restrictions.

- For PSSCR<sub>ESL</sub> = 0 and power-saving level 0000, no thread state is lost.

- There must be a power-saving level in which the Decrementer and all hypervisor resources are maintained as if the thread was not in power-saving mode, and in which sufficient information is maintained to allow the hypervisor to resume execution.

20

- The amount of state loss in a given level is less than or equal to the amount of state loss in the next higher level.

- The state of all read-only resources, SMFCTRL<sub>E</sub>, and the URMOR in an SMF-enabled system or the HRMOR in an SMF-disabled system is always maintained.

#### — Programming Note –

I

For the power-saving level corresponding to the second item above, if the state of the Decrementer were not maintained and updated as if the thread was not in power-saving mode, Decrementer exceptions would not reliably cause exit from this power-saving level even if Decrementer exceptions were enabled to cause exit.

## Section 3.3.2.1 Power-Saving Mode Instruction

------ End text ------

Add SMFCTRL[UDEE] to the list of controls for powersaving exit and note that the ultravisor must not execute stop. (The latter choice was made because of the difficulty for the design to wake up in the right state in the prevented circumstances.) Move the two p-notes to section 3.3.2.2.

----- Begin text -----

The thread remains in power-saving mode until either a System Reset exception or certain other events occur. The events that may cause exit from power-saving mode are specified by  $PSSCR_{EC}$ ,  $LPCR_{PECE}$ , and  $SMFCTRL_{UDEE}$ . If the event that causes the exit is a System Reset, Machine Check, or Hypervisor Maintenance exception, resource state that would be lost if the exception occurred when the thread was not in power-saving mode may be lost.

An attempt to execute this instruction in Suspended state will result in a TM Bad Thing type Program interrupt.

This instruction should not be executed in ultravisor state because that scenario may not be thoroughly verified.

----- End text -----

## Section 3.3.2.2 Entering and Exiting Power-Saving Mode

Add a high level description of how SMF/ultravisor relates to power saving. Include UDEE in the possible exit causes. Note that this also tries to fix integration errors from RFC 2492B by moving p-notes from the stop description to this section. Note that "stop" should be in the appropriate font (fixed here w/o change bars).

----- Begin text -----