T2P9D01 Mainboard

User's Guide For System Configuration and Set Up

# **Table of Contents**

| COPYRIGHT AND DISCLAIMERS                   | 5  |

|---------------------------------------------|----|

| SAFETY INFORMATION                          | 6  |

| Electrical Safety                           | 6  |

| Operational Safety                          | 6  |

| NOTICES                                     | 7  |

| Federal Communications Commission Statement | 7  |

| Environmental Disposal Statements           | 7  |

| MAINBOARD SPECIFICATIONS                    | 8  |

| MAINBOARD OVERVIEW                          | 10 |

| Design                                      | 10 |

| Installation                                | 11 |

| Removal                                     | 11 |

| CPU INSTALLATION AND REMOVAL                | 12 |

| Background                                  | 12 |

| Installation                                | 13 |

| Removal                                     | 15 |

| RAM INSTALLATION AND REMOVAL                | 16 |

| Population Tables                           | 16 |

| Installation                                | 17 |

| Removal                                     | 17 |

| HEADERS AND CONNECTORS                      | 18 |

| Pin Numbering Conventions                   | 18 |

| Front Panel                                 | 19 |

| BMC Serial Console                | 21 |

|-----------------------------------|----|

| Trusted Platform Module Connector | 22 |

| FlexVer™ Connector                | 24 |

| OCC Mode                          | 26 |

| BMC External Reset Header         | 27 |

| BMC TTL Auxiliary Serial Header   | 28 |

| BMC Heartbeat Indicator Header    | 29 |

| Internal USB 3.0 Header           | 30 |

| BMC I2C Port 5                    | 32 |

| BMC I2C Port 6                    | 33 |

| Planar VPD Programming Header     | 34 |

| FPGA Programming Header           | 35 |

| FPGA Mode Switch 1                | 36 |

| FPGA Mode Switch 2                | 37 |

| PM8068 SAS Debug Connector        | 38 |

| 5V Power                          | 40 |

| CPU 1 Secure Mode Disable         | 41 |

| CPU 2 Secure Mode Disable         | 42 |

| PMBus Connector                   | 43 |

| CPU 1 Fan Header                  | 44 |

| CPU 2 Fan Header                  | 45 |

| Primary Chassis Fan Headers       | 46 |

| Secondary Chassis Fan Header      | 47 |

| FAN ZONES                         | 48 |

| Connections                       | 48 |

| Algorithm Description             | 48 |

| USAGE                             | 49 |

|                                   |    |

| Initial Power-On        | 49 |

|-------------------------|----|

| Selecting a Boot Medium | 49 |

| BMC Access              | 50 |

| Host Firmware Updates   | 50 |

| BMC Firmware Updates    | 50 |

| SUPPORT                 | 52 |

| Getting Help            |    |

|                         |    |

### Copyright and Disclaimers

#### Copyright © 2017 – 2018 Raptor Computing Systems, LLC. All Rights Reserved.

Product warranty or service will not be extended if: (1) the product is damaged by the consumer in any way, including any alterations that affect the operability of the feature or features being claimed under warranty and/or product service; or (2) the serial number of the product is defaced or missing.

RAPTOR COMPUTING SYSTEMS, LLC PROVIDES THIS MANUAL "AS IS" WITHOUT WARRANTY OF ANY KIND, EITHER EXPRESS OR IMPLIED, INCLUDING BUT NOT LIMITED TO THE IMPLIED WARRANTIES OR CONDITIONS OF MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE. IN NO EVENT SHALL RAPTOR COMPUTING SYSTEMS, LLC, ITS DIRECTORS, OFFICERS, MEMBERS, MANAGERS, EMPLOYEES OR AGENTS BE LIABLE FOR ANY INDIRECT, SPECIAL, INCIDENTAL, OR CONSEQUENTIAL DAMAGES (INCLUDING DAMAGES FOR LOSS OF PROFITS, LOSS OF BUSINESS, LOSS OF USE OR DATA, INTERRUPTION OF BUSINESS AND THE LIKE), EVEN IF RAPTOR COMPUTING SYSTEMS, LLC HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES ARISING FROM ANY DEFECT OR ERROR IN THIS MANUAL OR PRODUCT.

SPECIFICATIONS AND INFORMATION CONTAINED IN THIS MANUAL ARE FURNISHED FOR INFORMATIONAL USE ONLY, AND ARE SUBJECT TO CHANGE AT ANY TIME WITHOUT NOTICE, AND SHOULD NOT BE CONSTRUED AS A COMMITMENT BY RAPTOR COMPUTING SYSTEMS, LLC. RAPTOR COMPUTING SYSTEMS, LLC ASSUMES NO RESPONSIBILITY OR LIABILITY FOR ANY ERRORS OR INACCURACIES THAT MAY APPEAR IN THIS MANUAL, INCLUDING THE PRODUCTS AND SOFTWARE DESCRIBED IN IT.

Products and corporate names appearing in this manual may or may not be registered trademarks or copyrights of their respective companies, and are used only for identification or explanation and to the owners' benefit, without intent to infringe.

# Safety Information

#### **ELECTRICAL SAFETY**

- To reduce the risk of electric shock, disconnect the power cable before relocating or servicing the system.

- When adding or removing devices to or from the system, ensure that the power cables for the

devices are unplugged before the signal cables are connected. If possible, disconnect all power

cables from the existing system before you add a device.

- Before connecting or removing signal cables from the motherboard, ensure that all power cables are unplugged.

- Seek professional assistance before using an adapter or extension cord. These devices could interrupt the grounding circuit.

- Make sure that your power supply is set to the correct voltage in your area. If you are not sure about the voltage of the electrical outlet you are using, contact your local power company.

- If your power supply is not functioning, do not attempt to repair it. Contact a qualified service technician or your retailer.

#### OPERATIONAL SAFETY

- Before installing the motherboard or connecting devices to it, carefully read any and all provided manuals for the devices in question.

- Before using the product, make sure all cables are correctly connected and the power cables are not damaged. If you find any damage, contact your dealer immediately.

- To avoid short circuits, keep paper clips, screws, staples, and other foreign metallic objects away from connectors, slots, sockets and circuitry.

- Avoid dust, humidity, and temperature extremes. Do not locate the product in any area where it may become wet or damp.

- Place the product on a stable surface at all times.

- If you encounter technical problems with the product, contact a qualified service technician or your retailer.

### **Notices**

#### FEDERAL COMMUNICATIONS COMMISSION STATEMENT

This device complies with Part 15 of the FCC Rules. Operation is subject to the following two conditions:

- This device may not cause harmful interference, and

- This device must accept any interference received including interference that may cause undesired operation.

This equipment has been tested and found to comply with the limits for a Class B digital device, pursuant to Part 15 of the FCC Rules. These limits are designed to provide reasonable protection against harmful interference in a residential installation. This equipment generates, uses and can radiate radio frequency energy and, if not installed and used in accordance with manufacturer's instructions, may cause harmful interference to radio communications. However, there is no guarantee that interference will not occur in a particular installation. If this equipment does cause harmful interference to radio or television reception, which can be determined by turning the equipment off and on, the user is encouraged to try to correct the interference by one or more of the following measures:

- Reorient or relocate the receiving antenna.

- Increase the separation between the equipment and receiver.

- Connect the equipment to an outlet on a circuit different from that to which the receiver is connected.

- Consult the dealer or an experienced radio/TV technician for help.

#### **ENVIRONMENTAL DISPOSAL STATEMENTS**

DO NOT throw the motherboard in municipal waste. This product has been designed to enable proper reuse of parts and recycling. This symbol of the crossed out wheeled bin indicates that the product (electrical and electronic equipment) should not be placed in municipal waste. Check local regulations for disposal of electronic products.

DO NOT throw the mercury-containing button cell battery in municipal waste. This symbol of the crossed out wheeled bin indicates that the battery should not be placed in municipal waste.

# Mainboard Specifications

|                        |                      | 2x IBM POWER9 "Sforza" Socket (LGA 2601)<br>4 - 24 core IBM POWER9 Processors<br>High speed XBUS interconnect |  |  |  |

|------------------------|----------------------|---------------------------------------------------------------------------------------------------------------|--|--|--|

| Core Logic             |                      | Direct Attach PCIe                                                                                            |  |  |  |

| Form Factor            |                      | EATX, 12" x 13"                                                                                               |  |  |  |

| System Features        | Fan Control          | Υ                                                                                                             |  |  |  |

|                        | Nominal Fan Zones    | 3                                                                                                             |  |  |  |

|                        | Fan Connectors       | 7                                                                                                             |  |  |  |

|                        | Fan Control Driver   | MAX31785 / AST2500                                                                                            |  |  |  |

|                        | Rack Ready           | Υ                                                                                                             |  |  |  |

|                        | Front Panel Header   | SuperMicro Compatible                                                                                         |  |  |  |

|                        | TPM Header           | LPC / I2C                                                                                                     |  |  |  |

|                        | SMBus Header         | Y                                                                                                             |  |  |  |

|                        | BMC                  | Υ                                                                                                             |  |  |  |

|                        | BMC Type             | OpenBMC Compatible (AST2500)                                                                                  |  |  |  |

|                        | FlexVer™ Ready       | Υ                                                                                                             |  |  |  |

| Memory                 | Total Slots          | 16 (4 channels per CPU)                                                                                       |  |  |  |

|                        | Capacity             | 2TB maximum                                                                                                   |  |  |  |

|                        | Memory Type          | DDR4 1600/1866/2133/2400/2666                                                                                 |  |  |  |

|                        | Memory Features      | ECC                                                                                                           |  |  |  |

|                        | Module Sizes         | 8GB, 16GB, 32GB, 64GB, 128GB (RDIMM)                                                                          |  |  |  |

| <b>Expansion Slots</b> | Total PCle Slots     | 5                                                                                                             |  |  |  |

|                        | Total OCuLink Ports  | 1                                                                                                             |  |  |  |

|                        | PCIe Generation      | 1,2,3,4                                                                                                       |  |  |  |

|                        | CAPI 2 Capable Slots | 3 x16 slots                                                                                                   |  |  |  |

| Storage                | Microsemi PM8068     | 4 SAS (iPASS+)                                                                                                |  |  |  |

|                        | (optional)           | 4 SAS/SATA                                                                                                    |  |  |  |

| Networking             | Broadcom BCM5719     | 2 host GbE                                                                                                    |  |  |  |

|                        |                      | NCSI-SI BMC link                                                                                              |  |  |  |

| Graphics               | AST2500              | VGA                                                                                                           |  |  |  |

| USB                    | TI TUSB7430          | 2x USB3.0 ports on rear panel                                                                                 |  |  |  |

|                        |                      | 2x USB3.0 ports on internal header                                                                            |  |  |  |

| Serial                 | Host                 | 1x RS232 port on rear panel                                                                                   |  |  |  |

| BMC                        | 1x RS232 port on internal header    |  |  |  |

|----------------------------|-------------------------------------|--|--|--|

|                            | 1x TTL port on internal header      |  |  |  |

| Environmental Requirements | Operation: 10°C - 35°C              |  |  |  |

|                            | Storage: -40°C - 70°C               |  |  |  |

|                            | Humidity: 20% - 90%, non-condensing |  |  |  |

NOTE: Specifications are subject to change without notice.

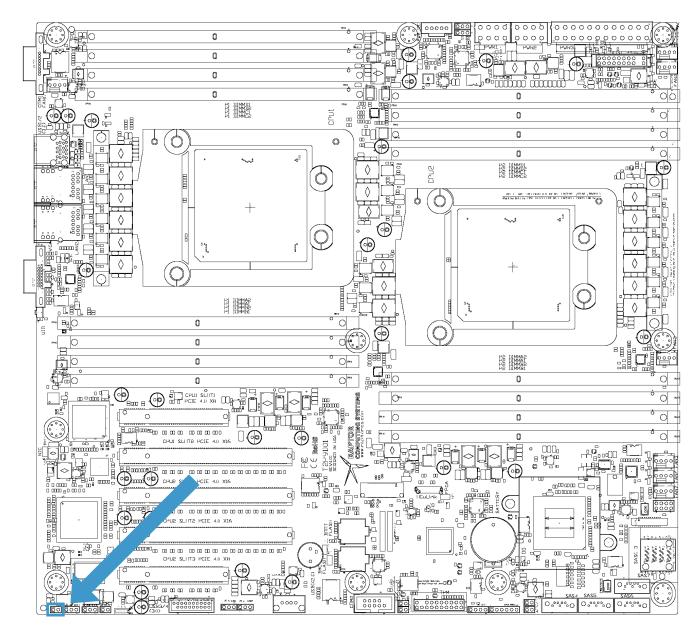

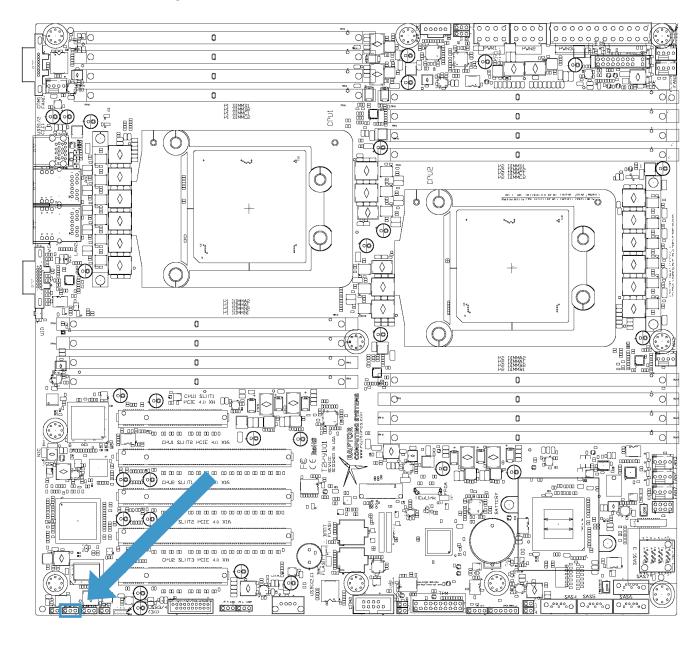

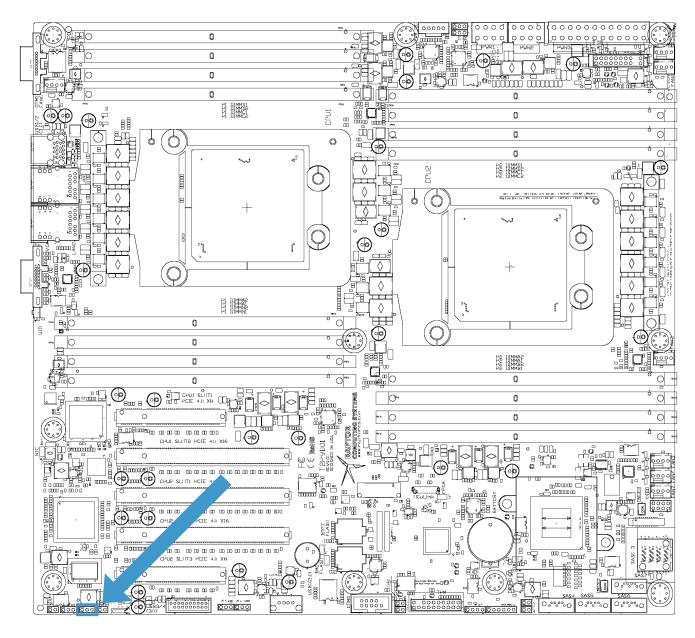

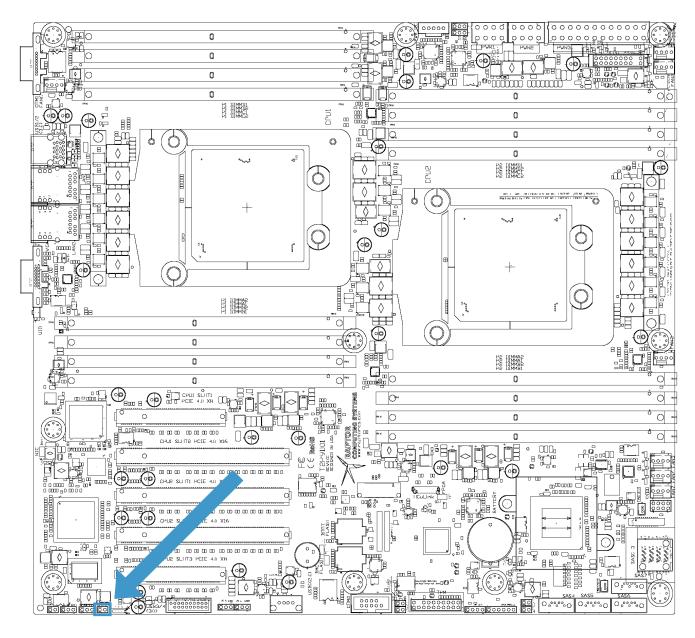

### Mainboard Overview

#### **DESIGN**

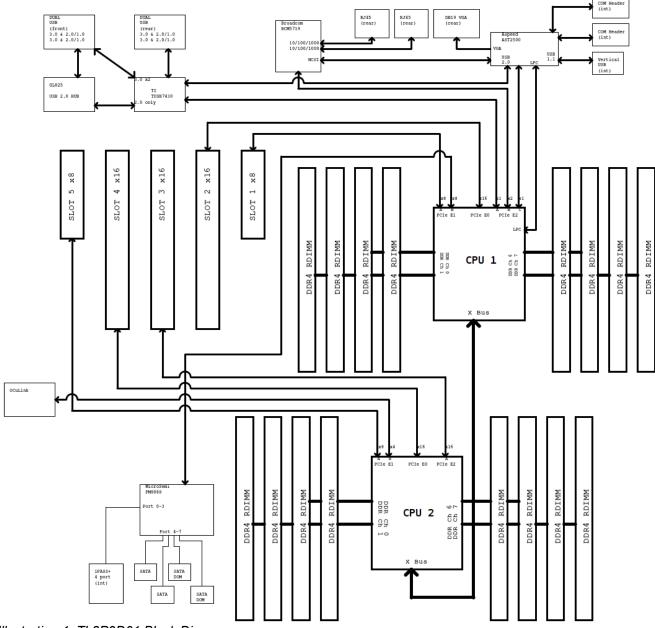

The T2P9D01 has been specifically designed for applications requiring high security, high I/O capability, and large amounts of processing capability. PCle slots and peripherals are directly connected to each CPU, therefore two CPUs must be installed to use all PCle slots.

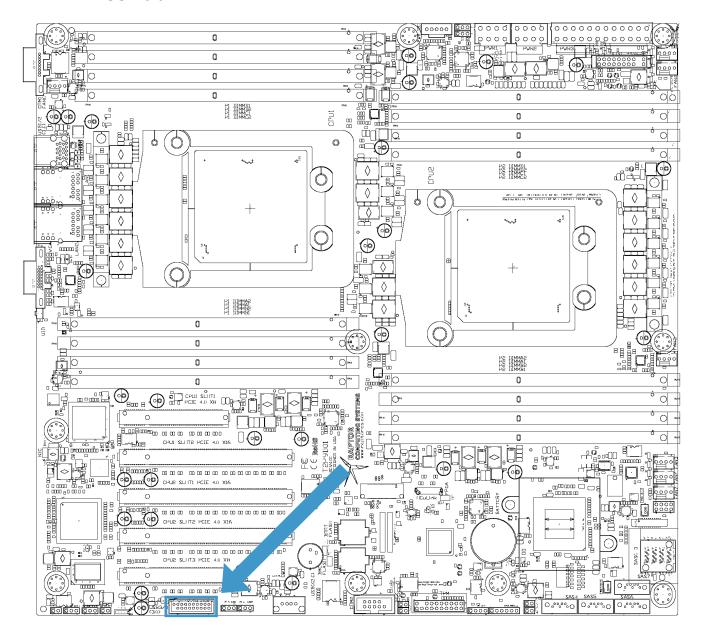

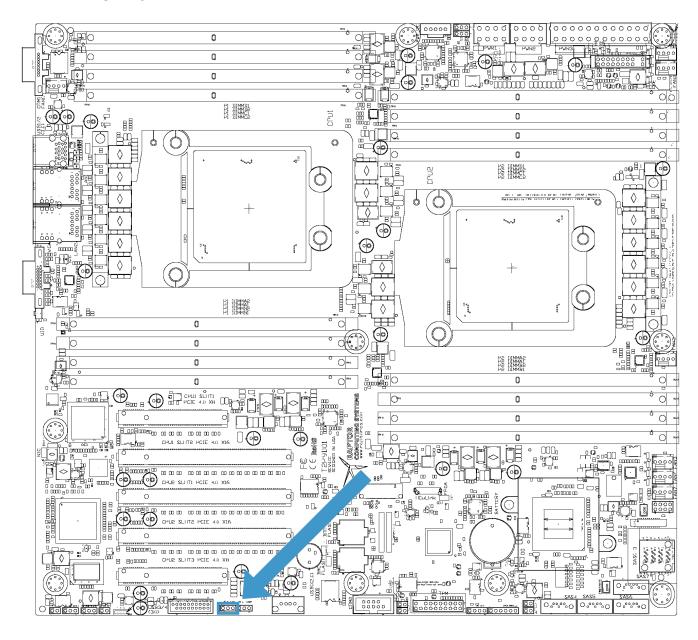

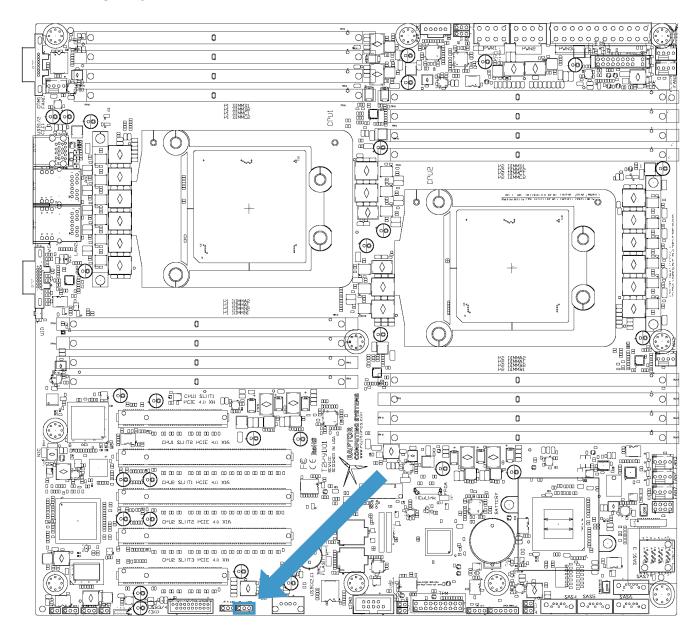

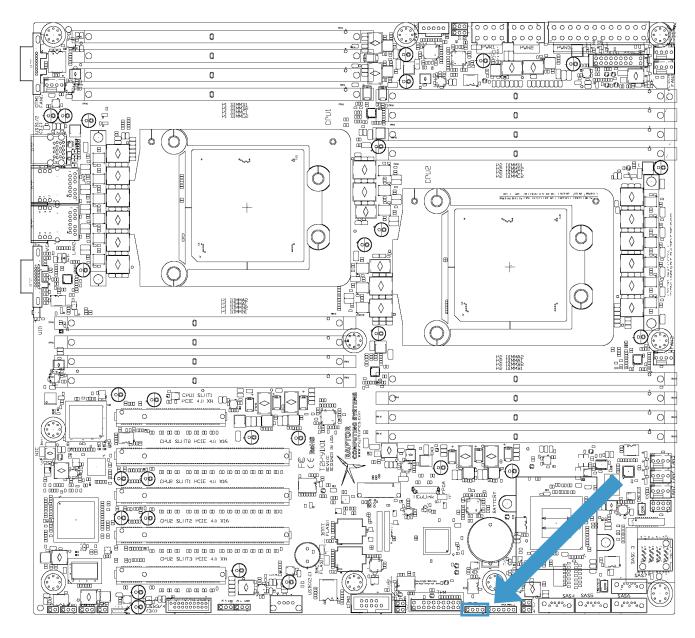

Illustration 1: TL2P9D01 Block Diagram

#### INSTALLATION

**NOTE:** Before you install this mainboard into your chassis, study the pattern of mounting studs, rear panel slots, and internal chassis components to ensure the mainboard fits correctly. There are 10 mounting holes available on the T2P9D01; ensure that your chassis provides studs for all 10 for maximum reliability and longevity of the mainboard.

**NOTE:** Installation of the mainboard should take place in a static-controlled environment using appropriate anti-static measures. Failure to follow these precautions could result in permanent damage to the mainboard and attached components.

Begin installation by examining your chassis. If there is an existing I/O shield in your chassis, remove it by gently striking it from the outside of your chassis; it should pop free. Align the new I/O shield inside your chassis so that the ridges on the I/O shield point away from the interior of your chassis; then, gently but firmly snap the new I/O shield into place in the rear of your chassis.

Carefully place the mainboard inside the chassis, ensuring that the I/O ports are aligned with the corresponding holes in the I/O shield. Gently press the mainboard into the I/O shield until the mounting holes are aligned with the chassis studs. Secure the mainboard with one screw in the lower right corner, followed by one in the upper left corner, then install the remaining screws. Torque all mainboard mounting screws to 7 ft-lbs (0.8N-m).

**WARNING**: There are fragile electronic components located on the entire bottom surface of the mainboard, including near the mainboard mounting holes. Ensure that the mainboard is aligned with the studs *before* allowing any part of the rear surface to contact the mounting studs; also ensure that the mainboard does not slide on the studs once positioned. Failure to follow these instructions could result in severe damage to the mainboard. If you believe you have damaged one or more parts on the bottom of the mainboard, but have not yet applied power, **stop** and remove the mainboard *without* applying power. Inspect the mainboard for mechanical damage, and if present return the mainboard for repair service.

#### **REMOVAL**

Begin by moving the chassis to a static-controlled environment. Before removing the mainboard, remove all attached cables, peripherals, and RAM. Ensure that both CPUs and heatsinks have been removed, and that both protective socket covers are in place. Carefully loosen and remove all screws, saving the lower right hand corner for last. Gently lift the side of the mainboard farthest from the I/O shield, then slide the ports out of the I/O shield. Do not allow the mainboard to fall onto or contact the chassis mounting studs at this point. Carefully remove the mainboard from the chassis. If the mainboard is to be returned for service, immediately place it in an appropriately sized anti-static bag.

### **CPU Installation and Removal**

#### BACKGROUND

The POWER9 CPU uses a unique retention mechanism designed to center-load the CPU in the socket and ensure good contact in the area of the central lands. This mechanism is spring loaded; a single 5/32" hex screw engages and disengages the retention system.

The heatsink assemblies you have received may have had the screw tighten or loosen in transit. After placing the heatsink on the CPU per the following instructions, visually inspect the two latching prongs protruding from the load frame assembly. If these prongs are not vertical, loosen the retention screw of the heatsink assembly and gently reposition the heatsink, watching for the latching prongs to move into a vertical position.

Illustration 2: Correct Retention Mechanism Prong Alignment (Unlocked)

**NOTE:** Incorrectly positioned locking pins will cause the heatsink to start to tilt as the retention screw is tightened. If this happens, **immediately stop tightening the screw**, carefully loosen the retention screw, and double-check the prong and pin alignment before attempting to reattach the heatsink. In some cases, removing and re-placing the heatsink is the easiest method to allow it to seat correctly.

#### **INSTALLATION**

**WARNING:** Both the CPUs and the mainboard are static sensitive. Installation and removal of either CPU must take place in an appropriate anti-static environment.

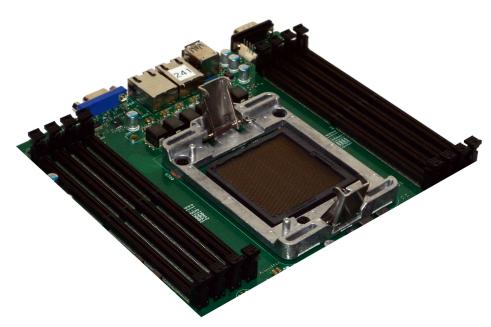

Illustration 3: Socket as Shipped

Carefully remove the protective cover, making sure not to touch any of the exposed socket pins.

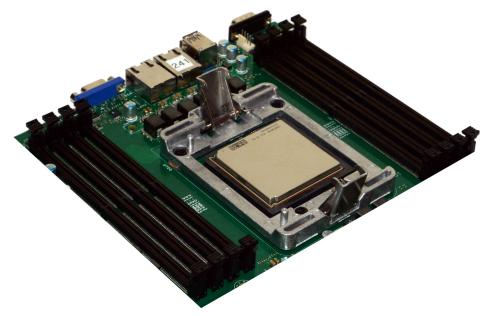

Illustration 4: Remove Protective Cover

Align the notches of the CPU with the protrusions on the socket, then carefully place the CPU in the socket. If no indium pad is present on the bottom of the heatsink assembly, carefully center an indium pad on top of the CPU.

Illustration 5: Align Notches and Carefully Place CPU in Socket

Place the heatsink assembly on top of the CPU, following instructions given earlier.

Illustration 6: Align Pins and Place Heatsink on CPU

Using a 5/32" hex driver fully inserted into the retention mechanism screw, tighten the retention mechanism screw by turning the driver clockwise until a hard stop has been reached.

Illustration 7: Tighten Retention Scew until Hard Stop

Your CPU now is correctly installed. If you have a second CPU, repeat this process for the other socket.

#### REMOVAL

Removal of the heatsink and CPU follows the installation procedure given above, only in reverse. Start with step 5, turning the hex driver counterclockwise, and end with step 1, replacing the socket protective cover into postion over the socket.

**WARNING:** Before attempting to remove the heatsink, ensure the mainboard has been placed horizontal to the ground. Failing to do so could cause the CPU to fall out of the socket, causing damage to the CPU, the CPU socket, and any components located below the CPU.

## **RAM Installation and Removal**

#### **POPULATION TABLES**

| Quantity |    |             |    |    |    |    | S  | lot Po      | opula                   | tion |    |    |    |    |    |    |

|----------|----|-------------|----|----|----|----|----|-------------|-------------------------|------|----|----|----|----|----|----|

|          |    | Processor 1 |    |    |    |    |    | Processor 2 |                         |      |    |    |    |    |    |    |

|          | A1 | B1          | C1 | D1 | A2 | B2 | C2 | D2          | A1                      | B1   | C1 | D1 | A2 | B2 | C2 | D2 |

| 1 DIMM   |    | X           |    |    |    |    |    |             |                         | ·    | •  |    | •  |    |    |    |

| 2 DIMMs  |    | X           |    | Х  |    |    |    |             |                         |      |    |    |    |    |    |    |

| 3 DIMMs  | Х  | X           |    | Х  |    |    |    |             |                         |      |    |    |    |    |    |    |

| 4 DIMMs  | Х  | X           | Х  | Х  |    |    |    |             | December Net In stell   |      |    |    |    |    |    |    |

| 5 DIMMs  | Х  | X           | Х  | Х  | Х  |    |    |             | Processor Not Installed |      |    |    |    |    |    |    |

| 6 DIMMs  | Х  | X           | Х  | Х  | Х  |    |    | Х           |                         |      |    |    |    |    |    |    |

| 7 DIMMs  | Х  | X           | Х  | Х  | Х  | Х  |    | Х           |                         |      |    |    |    |    |    |    |

| 8 DIMMs  | Х  | Х           | Х  | Х  | Х  | Х  | Х  | Х           |                         |      |    |    |    |    |    |    |

| 1 DIMM   |    | X           |    |    |    |    |    |             |                         |      |    |    |    |    |    |    |

| 2 DIMMs  |    | Х           |    |    |    |    |    |             |                         | Х    |    |    |    |    |    |    |

| 3 DIMMs  |    | X           |    | Х  |    |    |    |             |                         | Х    |    |    |    |    |    |    |

| 4 DIMMs  |    | Х           |    | Х  |    |    |    |             |                         | Х    |    | Х  |    |    |    |    |

| 5 DIMMs  | Х  | X           |    | Х  |    |    |    |             |                         | Х    |    | Х  |    |    |    |    |

| 6 DIMMs  | Х  | Х           |    | Х  |    |    |    |             | Х                       | Х    |    | Х  |    |    |    |    |

| 7 DIMMs  | Х  | X           | Х  | Х  |    |    |    |             | Х                       | Х    |    | Х  |    |    |    |    |

| 8 DIMMs  | Х  | Х           | Х  | Х  |    |    |    |             | Х                       | Х    | Х  | Х  |    |    |    |    |

| 9 DIMMs  | Х  | X           | Х  | Х  |    | Х  |    |             | Х                       | Х    | Х  | Х  |    |    |    |    |

| 10 DIMMs | Х  | X           | Х  | Х  |    | Х  |    |             | Х                       | Х    | Х  | Х  |    | Х  |    |    |

| 11 DIMMs | Х  | X           | Х  | Х  |    | Х  |    | Х           | Х                       | Х    | Х  | Х  |    | Х  |    |    |

| 12 DIMMs | Х  | Х           | Х  | Х  |    | Х  |    | Х           | Х                       | Х    | Х  | Χ  |    | Х  |    | Х  |

| 13 DIMMs | Х  | Х           | Х  | Х  | Х  | Х  |    | Х           | Х                       | X    | Х  | Χ  |    | Х  |    | Х  |

| 14 DIMMs | Х  | Х           | Х  | Х  | Х  | Х  |    | Х           | Х                       | Х    | Х  | Χ  | Х  | Х  |    | Х  |

| 15 DIMMs | Х  | Х           | Х  | Х  | Х  | Х  | Х  | Х           | Х                       | Х    | Х  | Χ  | Х  | Х  |    | Х  |

| 16 DIMMs | Х  | Х           | Х  | Х  | Х  | Х  | Х  | Х           | Х                       | Х    | Х  | Х  | Х  | Х  | Х  | Х  |

(X) denotes memory DIMM is installed in indicated slot

#### INSTALLATION

For maximum performance under typical workloads, RAM should be populated according to the table above.

Using proper anti-static procedures, locate the slot in which you want to install RAM, then gently move the two retaining prongs away from the center of the slot until they reach a hard stop. Grasping the memory DIMM by the edges, align the notch on the memory DIMM with the key in the slot, then firmly and evenly press the DIMM into place while holding the DIMM at a 90° angle to the mainboard. The DIMM is properly seated when both retaining prongs move inward and contact the sides of the DIMM. Do not touch the electrical contacts on the memory DIMM as this may induce corrosion, leading to poor connections and unreliable operation.

**WARNING:** If a DIMM will not fully seat, or tilts to one side, **stop**. Remove the DIMM and double-check the location of the notch versus the slot key. If the DIMM still will not seat, double check that the type of memory is correct. The T2P9D01 only accepts full-size 288-pin DDR4 DIMMs, and other types of memory will not seat or function. DO NOT attempt to force a DIMM into a slot as this may cause permanent damage to the RAM, CPU, and/or mainboard.

**WARNING:** Do not attempt to install memory DIMMs in an improperly mounted mainboard. Due to the pressure required to properly seat a DIMM, mainboard flex tolerances could be exceeded if one or more mounting studs is missing. Exceeding flex tolerances may cause irreparable damage to the mainboard.

#### REMOVAL

Locate the DIMM you wish to remove, then, using proper anti-static procedures, gently move the two retaining prongs away from the center of the slot until they reach a hard stop. The memory DIMM will partially unseat from the slot, and may be fully removed by gently and evenly pulling away from the mainboard while grasping the DIMM by its two short edges. Do not touch the electrical contacts on the memory DIMM as this may induce corrosion and lead to poor connections and unreliable operation.

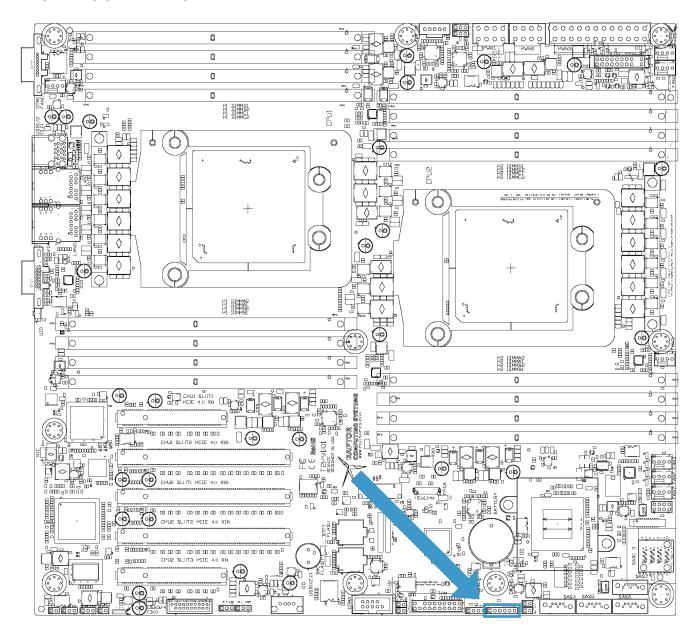

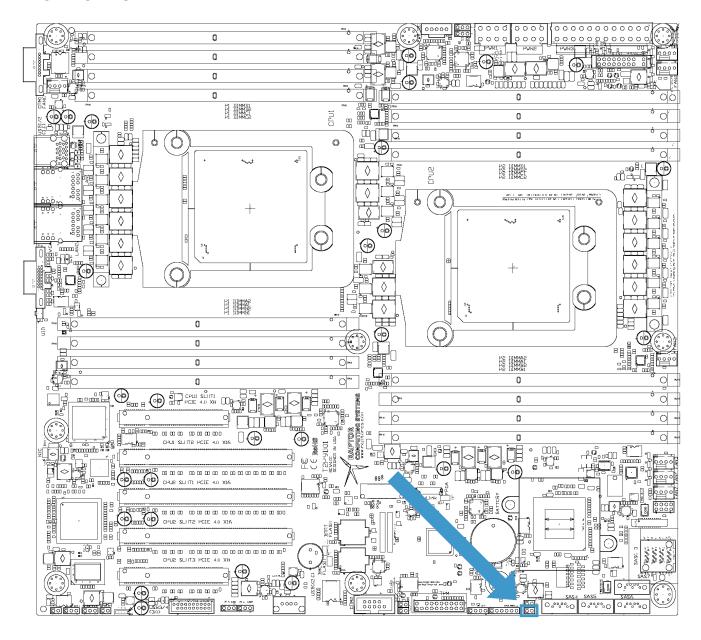

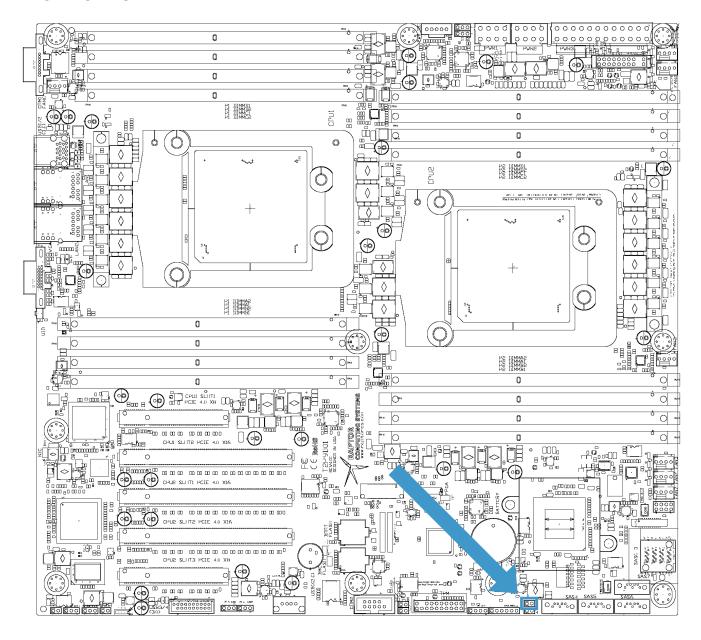

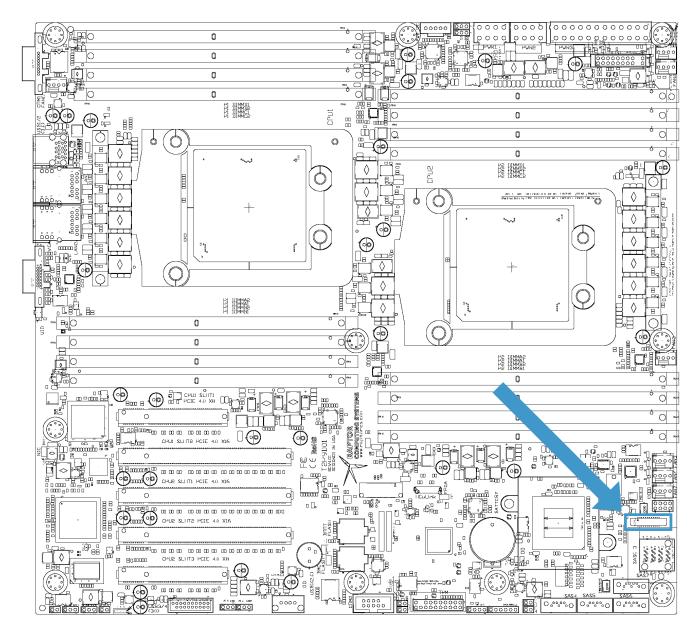

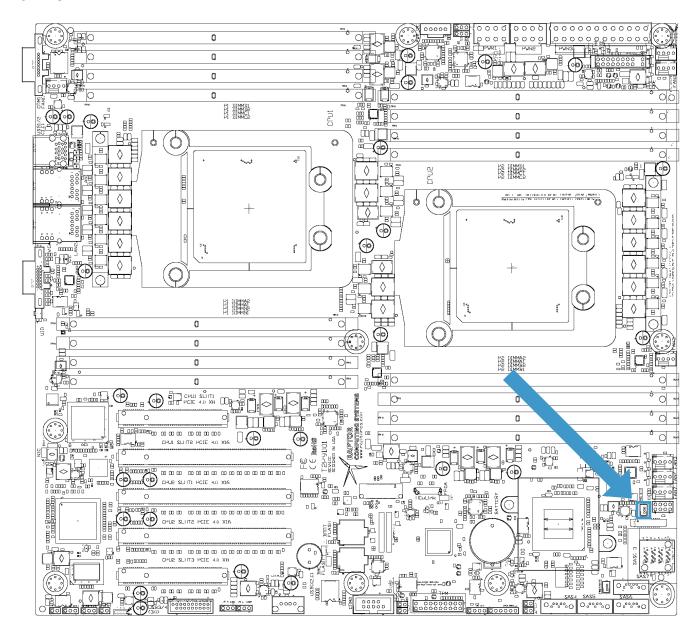

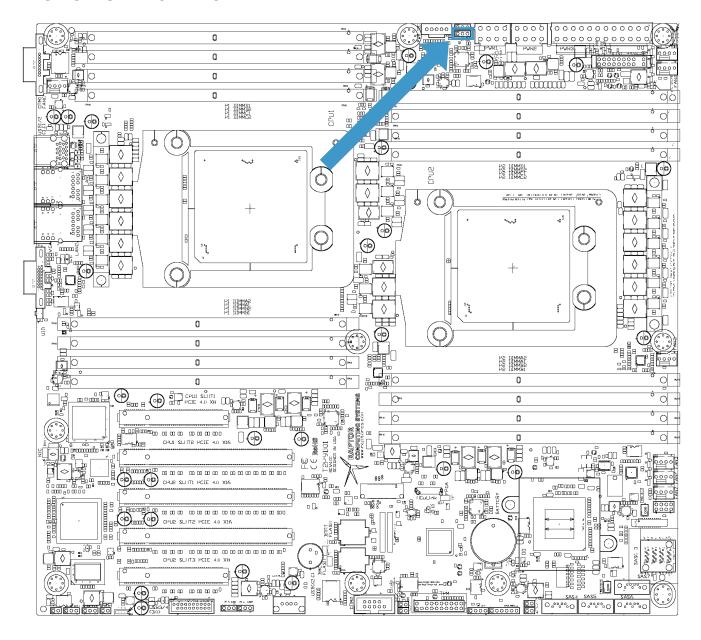

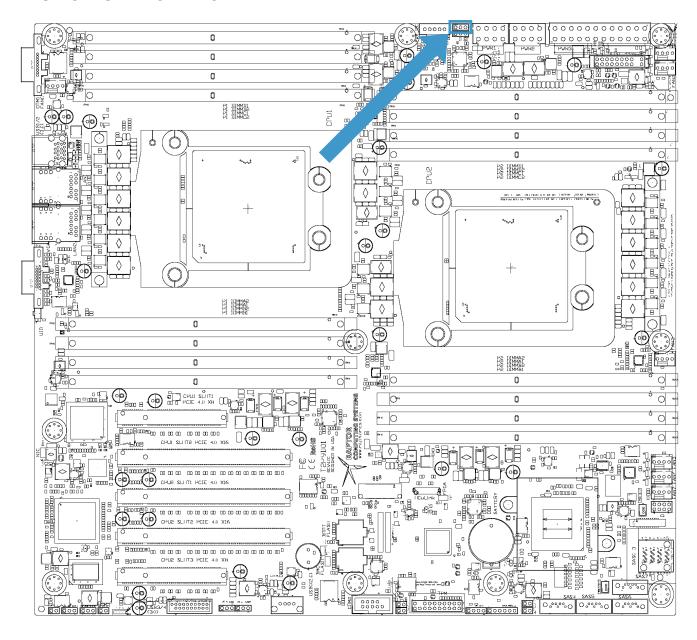

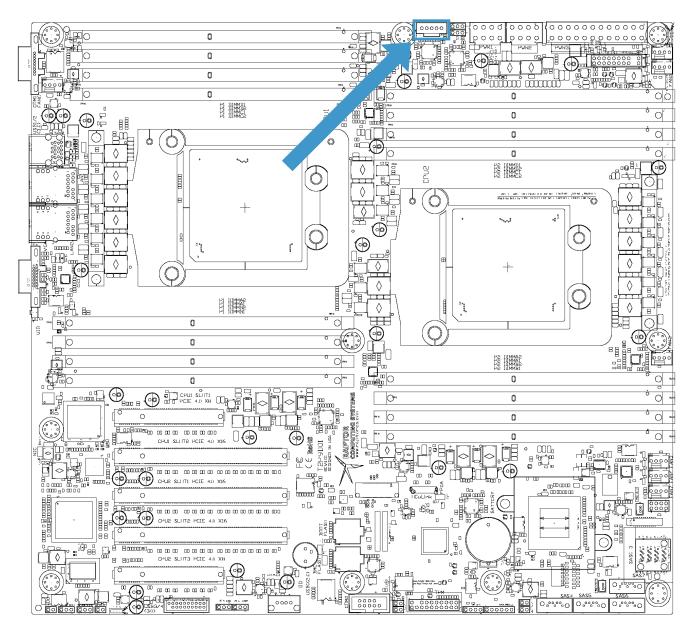

### **Headers and Connectors**

#### PIN NUMBERING CONVENTIONS

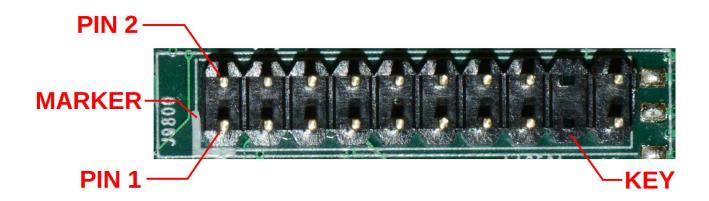

Illustration 8: Dual Row Header with Annotated Pins, Marker, and Key

All headers on the TLP9D01 follow a standard layout, with pin 1 being denoted with a white silkscreen marking. Dual row headers follow the numbering convention shown above, where all even pins are on one side of the header and all odd pins are on the other. Single row headers use a monotonically increasing pin number, starting from pin 1. Key pins are not physically present, but are still counted as pins in the numbering scheme.

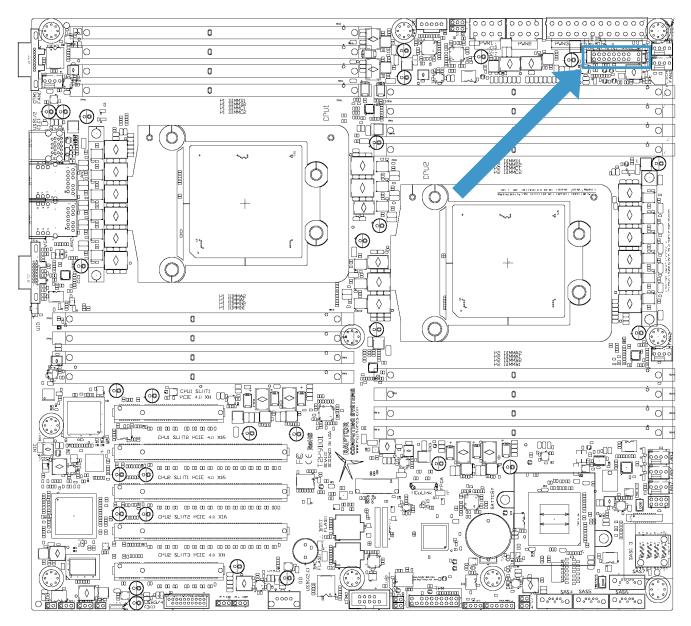

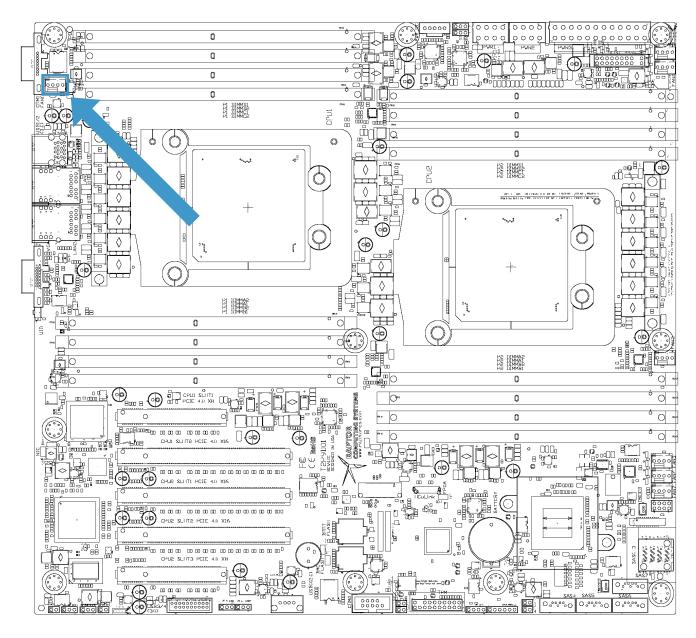

#### **FRONT PANEL**

| J9800 |                                 |     |                                     |  |  |  |  |

|-------|---------------------------------|-----|-------------------------------------|--|--|--|--|

| Pin   | Function                        | Pin | Function                            |  |  |  |  |

| 1     | Power button (active low)       | 2   | Ground                              |  |  |  |  |

| 3     | Reset button (active low)       | 4   | Ground                              |  |  |  |  |

| 5     | +3.3V (main power)              | 6   | Fan fail LED cathode                |  |  |  |  |

| 7     | LED Anode +3.3V (main power)    | 8   | Fan Fail LED Anode (+5V main power) |  |  |  |  |

| 9     | LED Anode +3.3V (standby power) | 10  | NIC 2 link / activity LED cathode   |  |  |  |  |

| 11    | LED Anode +3.3V (standby power) | 12  | NIC 1 link / activity LED cathode   |  |  |  |  |

| 13 | Identify button (active low) | 14 | HDD activity LED cathode |

|----|------------------------------|----|--------------------------|

| 15 | +3.3V (main power)           | 16 | Power LED cathode        |

| 17 | KEY                          | 18 | KEY                      |

| 19 | NMI button (active low)      | 20 | Ground                   |

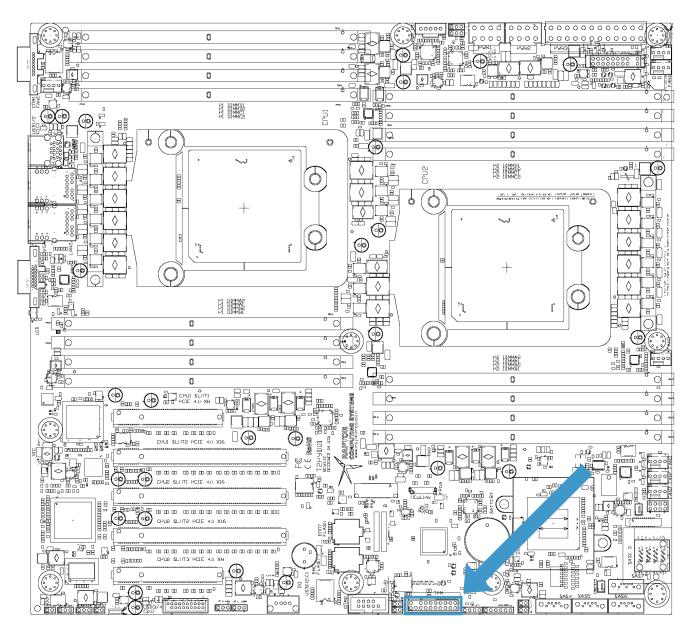

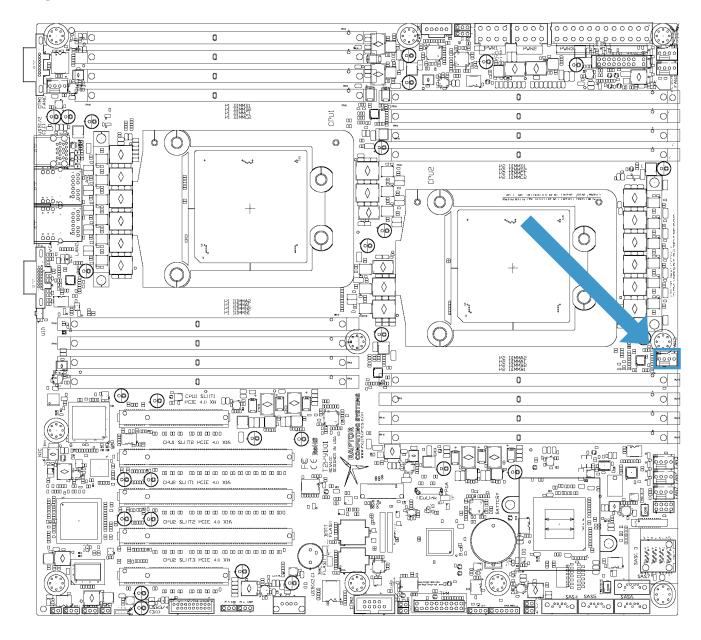

#### **BMC SERIAL CONSOLE**

| J7701 |          |     |          |  |  |  |  |

|-------|----------|-----|----------|--|--|--|--|

| Pin   | Function | Pin | Function |  |  |  |  |

| 1     | DCD      | 2   | RXD      |  |  |  |  |

| 3     | TXD      | 4   | DTR      |  |  |  |  |

| 5     | Ground   | 6   | DSR      |  |  |  |  |

| 7     | RTS      | 8   | CTS      |  |  |  |  |

| 9     | NRI      | 10  | KEY      |  |  |  |  |

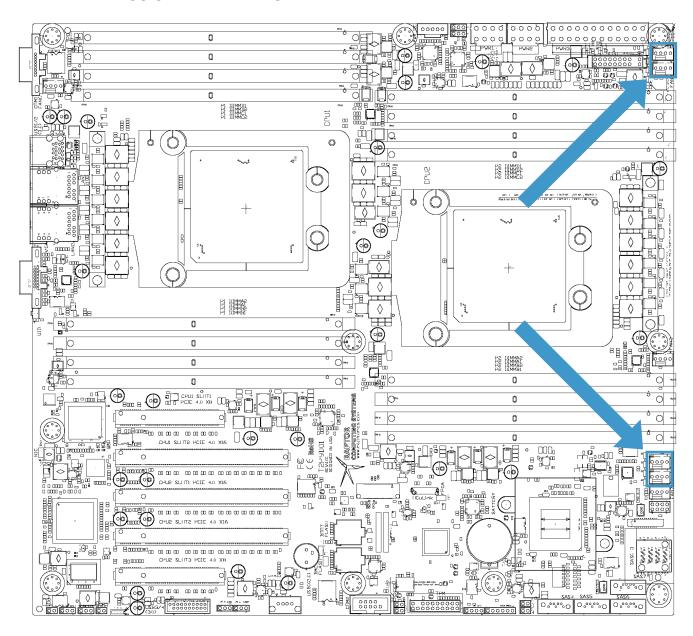

#### TRUSTED PLATFORM MODULE CONNECTOR

| J1010 | J10105                   |     |                          |  |  |  |  |  |  |

|-------|--------------------------|-----|--------------------------|--|--|--|--|--|--|

| Pin   | Function                 | Pin | Function                 |  |  |  |  |  |  |

| 1     | LPC clock                | 2   | Ground                   |  |  |  |  |  |  |

| 3     | LPC frame (active low)   | 4   | KEY                      |  |  |  |  |  |  |

| 5     | TPM reset (active low)   | 6   | N/C                      |  |  |  |  |  |  |

| 7     | LPC address / data bit 3 | 8   | LPC address / data bit 2 |  |  |  |  |  |  |

| 9     | +3.3V (main power)       | 10  | LPC address / data bit 1 |  |  |  |  |  |  |

| 11    | LPC address / data bit 0 | 12  | Ground                   |  |  |  |  |  |  |

| 13    | I2C clock                | 14  | I2C data                 |  |  |  |  |  |  |

| 15 | +3.3V (standby power)    | 16 | LPC serial IRQ           |

|----|--------------------------|----|--------------------------|

| 17 | Ground                   | 18 | N/C                      |

| 19 | Window open (active low) | 20 | BMC GPIO B3 (active low) |

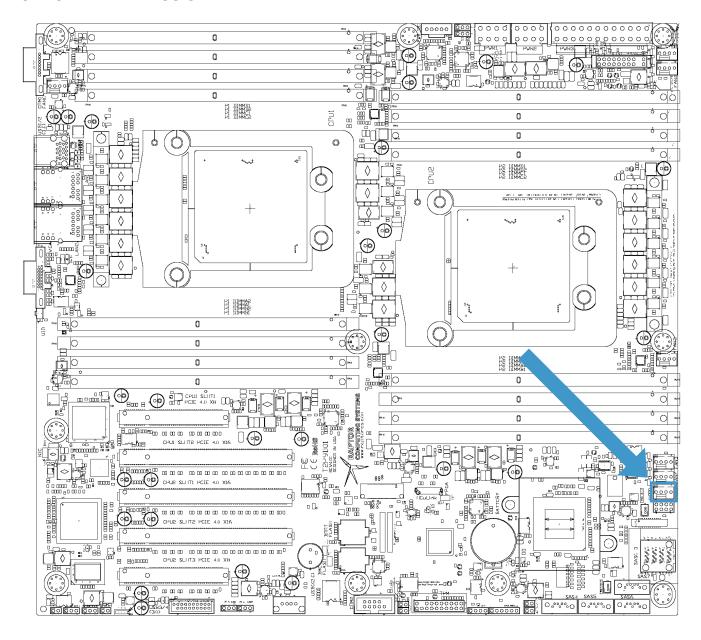

#### **FLEXVER™ CONNECTOR**

| J1011 | J10111                            |     |                                       |  |  |  |  |  |

|-------|-----------------------------------|-----|---------------------------------------|--|--|--|--|--|

| Pin   | Function                          | Pin | Function                              |  |  |  |  |  |

| 1     | RTC battery (+3.0V)               | 2   | Ground                                |  |  |  |  |  |

| 3     | +3.3V (standby power)             | 4   | Ground                                |  |  |  |  |  |

| 5     | +3.3V (main power)                | 6   | Module presence detect 1 (active low) |  |  |  |  |  |

| 7     | Integrity loop 0                  | 8   | Integrity loop 0                      |  |  |  |  |  |

| 9     | LPC address / data bit 3 (secure) | 10  | LPC address / data bit 0 (platform)   |  |  |  |  |  |

| 11    | LPC address / data bit 2 (secure) | 12  | LPC address / data bit 1 (platform)   |  |  |  |  |  |

| 13 | LPC address / data bit 1 (secure)        | 14 | LPC address / data bit 2 (platform)        |

|----|------------------------------------------|----|--------------------------------------------|

| 15 | LPC address / data bit 0 (secure)        | 16 | LPC address / data bit 3 (platform)        |

| 17 | LPC serial IRQ (secure)                  | 18 | LPC serial IRQ (platform)                  |

| 19 | LPC frame (active low, secure)           | 20 | LPC frame (active low, platform)           |

| 21 | CPU 0 presence detect (active low)       | 22 | CPU 1 presence detect (active low)         |

| 23 | LPC clock (secure)                       | 24 | LPC clock (platform)                       |

| 25 | LPC reset (active low, secure)           | 26 | LPC reset (active low, platform)           |

| 27 | BMC SPI MOSI (secure)                    | 28 | BMC SPI clock (platform)                   |

| 29 | BMC SPI clock (secure)                   | 30 | BMC SPI MOSI (platform)                    |

| 31 | BMC SPI MISO (secure)                    | 32 | BMC SPI MISO (platform)                    |

| 33 | BMC SPI chip select (active low, secure) | 34 | BMC SPI chip select (active low, platform) |

| 35 | N/C                                      | 36 | Module presence detect 2 (active low)      |

| 37 | Integrity loop 1                         | 38 | Integrity loop 1                           |

| 39 | Force FSI secure mode (active high)      | 40 | Platform reset (active low)                |

|    |                                          |    |                                            |

#### **OCC MODE**

| J6912 |                        |     |                          |  |

|-------|------------------------|-----|--------------------------|--|

| Pin   | Function               | Pin | Function                 |  |

| 1     | OCC alert (active low) | 2   | Ground (current limited) |  |

#### **BMC EXTERNAL RESET HEADER**

| J7000 | J7000    |     |                        |  |

|-------|----------|-----|------------------------|--|

| Pin   | Function | Pin | Function               |  |

| 1     | N/C      | 2   | BMC reset (active low) |  |

| 3     | Ground   |     |                        |  |

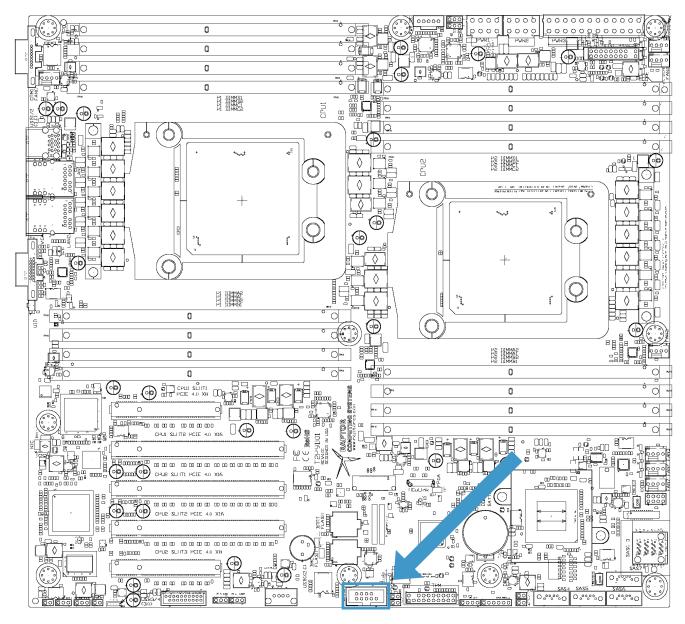

#### **BMC TTL AUXILIARY SERIAL HEADER**

| J10116 |                    |     |                    |

|--------|--------------------|-----|--------------------|

| Pin    | Function           | Pin | Function           |

| 1      | Ground             | 2   | BMC COM2 RXD (TTL) |

| 3      | BMC COM2 TXD (TTL) |     |                    |

#### **BMC HEARTBEAT INDICATOR HEADER**

| J10114 |          |     |                           |  |

|--------|----------|-----|---------------------------|--|

| Pin    | Function | Pin | Function                  |  |

| 1      | Ground   | 2   | BMC heartbeat LED cathode |  |

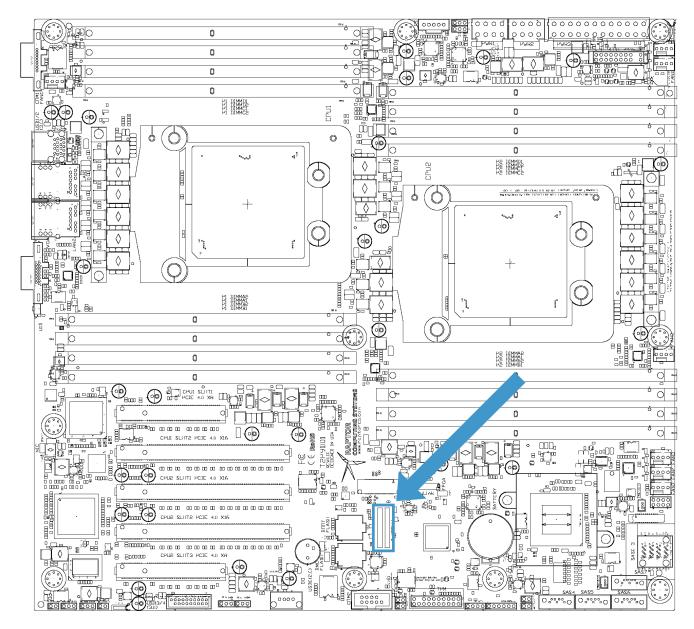

#### **INTERNAL USB 3.0 HEADER**

| J10106 |                                           |     |                                           |  |

|--------|-------------------------------------------|-----|-------------------------------------------|--|

| Pin    | Function                                  | Pin | Function                                  |  |

| 1      | +5.0V USB power (current limited)         | 2   | SuperSpeed RX (Port 4, negative polarity) |  |

| 3      | SuperSpeed RX (Port 4, positive polarity) | 4   | Ground                                    |  |

| 5      | SuperSpeed TX (Port 4, negative polarity) | 6   | SuperSpeed RX (Port 4, positive polarity) |  |

| 7      | Ground                                    | 8   | Hub (Port 1, negative polarity)           |  |

| 9      | Hub (Port 1, positive polarity)           | 10  | Ground                                    |  |

| 11 | Hub (Port 2, positive polarity)           | 12 | Hub (Port 2, negative polarity)           |

|----|-------------------------------------------|----|-------------------------------------------|

| 13 | Ground                                    | 14 | SuperSpeed TX (Port 3, positive polarity) |

| 15 | SuperSpeed TX (Port 3, negative polarity) | 16 | Ground                                    |

| 17 | SuperSpeed RX (Port 3, positive polarity) | 18 | SuperSpeed RX (Port 3, negative polarity) |

| 19 | +5.0V USB power (current limited)         | 20 | KEY                                       |

#### **BMC I2C PORT 5**

| J9602 | J9602       |     |          |  |  |

|-------|-------------|-----|----------|--|--|

| Pin   | Function    | Pin | Function |  |  |

| 1     | BMC I2C SCL | 2   | Ground   |  |  |

| 3     | BMC I2C SDA |     |          |  |  |

#### **BMC I2C PORT 6**

| J9603 |             |     |          |  |

|-------|-------------|-----|----------|--|

| Pin   | Function    | Pin | Function |  |

| 1     | BMC I2C SCL | 2   | Ground   |  |

| 3     | BMC I2C SDA |     |          |  |

#### PLANAR VPD PROGRAMMING HEADER

| J10104 |                       |     |          |

|--------|-----------------------|-----|----------|

| Pin    | Function              | Pin | Function |

| 1      | +3.3V (standby power) | 2   | SCL      |

| 3      | Ground                | 4   | SDA      |

#### FPGA PROGRAMMING HEADER

| J10107 |                               |     |                       |

|--------|-------------------------------|-----|-----------------------|

| Pin    | Function                      | Pin | Function              |

| 1      | Ground                        | 2   | SPI clock             |

| 3      | SPI MOSI                      | 4   | SPI MISO              |

| 5      | SPI slave select (active low) | 6   | +3.3V (standby power) |

#### **FPGA MODE SWITCH 1**

| J10109 |                                        |     |          |  |

|--------|----------------------------------------|-----|----------|--|

| Pin    | Function                               | Pin | Function |  |

| 1      | Mode enable bit 1 (active low, pullup) | 2   | Ground   |  |

# **FPGA MODE SWITCH 2**

| J7800 |                                        |     |          |  |

|-------|----------------------------------------|-----|----------|--|

| Pin   | Function                               | Pin | Function |  |

| 1     | Mode enable bit 2 (active low, pullup) | 2   | Ground   |  |

# PM8068 SAS DEBUG CONNECTOR

| J1  | J1                 |     |                  |  |  |

|-----|--------------------|-----|------------------|--|--|

| Pin | Function           | Pin | Function         |  |  |

| 1   | +1.8V (main power) | 2   | UART TX (Port 0) |  |  |

| 3   | UART TX (Port 1)   | 4   | UART RX (Port 0) |  |  |

| 5   | UART RX (Port 1)   | 6   | Ground           |  |  |

| 7   | Reset (active low) | 8   | JTAG TDI         |  |  |

| 9   | JTAG TMS           | 10  | JTAG TCLK        |  |  |

| 11 JTAG reset (active low) | 12 | JTAG TDO |

|----------------------------|----|----------|

|----------------------------|----|----------|

# **5V POWER**

| J19511 |                  |     |          |

|--------|------------------|-----|----------|

| Pin    | Function         | Pin | Function |

| 1      | +5V (main power) | 2   | Ground   |

| 3      | Ground           |     |          |

# **CPU 1 SECURE MODE DISABLE**

| J160 | J1600                                  |     |                                   |  |

|------|----------------------------------------|-----|-----------------------------------|--|

| Pin  | Function                               | Pin | Function                          |  |

| 1    | N/C                                    | 2   | Secure Mode Disable (active high) |  |

| 3    | +1.1V (standby power, current limited) |     |                                   |  |

# **CPU 2 SECURE MODE DISABLE**

| J4300 | J4300                                  |     |                                   |  |

|-------|----------------------------------------|-----|-----------------------------------|--|

| Pin   | Function                               | Pin | Function                          |  |

| 1     | N/C                                    | 2   | Secure Mode Disable (active high) |  |

| 3     | +1.1V (standby power, current limited) |     |                                   |  |

# **PMBUS CONNECTOR**

| J10103 |                                |     |          |  |

|--------|--------------------------------|-----|----------|--|

| Pin    | Function                       | Pin | Function |  |

| 1      | I2C SCL                        | 2   | I2C SDA  |  |

| 3      | Alert (active low, open drain) | 4   | Ground   |  |

| 5      | +3.3V (main power)             |     |          |  |

# **CPU 1 FAN HEADER**

| J7905 |                  |     |                   |

|-------|------------------|-----|-------------------|

| Pin   | Function         | Pin | Function          |

| 1     | Ground           | 2   | +12V (main power) |

| 3     | Tachometer input | 4   | PWM output        |

# **CPU 2 FAN HEADER**

| J7904 |                  |     |                   |

|-------|------------------|-----|-------------------|

| Pin   | Function         | Pin | Function          |

| 1     | Ground           | 2   | +12V (main power) |

| 3     | Tachometer input | 4   | PWM output        |

# PRIMARY CHASSIS FAN HEADERS

| J7900 | J7900 / J7901 / J7902 / J7903 |     |                   |  |

|-------|-------------------------------|-----|-------------------|--|

| Pin   | Function                      | Pin | Function          |  |

| 1     | Ground                        | 2   | +12V (main power) |  |

| 3     | Tachometer input              | 4   | PWM output        |  |

# SECONDARY CHASSIS FAN HEADER

| J10110 |                  |     |                   |

|--------|------------------|-----|-------------------|

| Pin    | Function         | Pin | Function          |

| 1      | Ground           | 2   | +12V (main power) |

| 3      | Tachometer input | 4   | PWM output        |

# Fan Zones

#### CONNECTIONS

The T2P9D01 supports three separate fan zones:

Zone 1: CPU 1 (1 fan) Zone 2: CPU 2 (1 fan)

Zone 3: Chassis (4 fans, fifth connector not monitored)

**NOTE**: At least one chassis fan providing airflow over the mainboard surface is strongly recommended. A minimum of 7CFM airflow over the SAS controller heatsink is required if the SAS controller option has been installed on the mainboard. Failure to provide adequate airflow over the SAS controller heatsink may result in system instability and premature failure.

# **ALGORITHM DESCRIPTION**

The stock fan control algorithm detects the presence or absence of CPU 2; if CPU 2 is missing, all fan controls for Zone 2 are deactivated and the Zone 2 fan headers are configured to run any attached fans at full speed.

On initial powerup, the functionality of all attached fans in each zone is tested. If any zone lacks at least one connected or functional fan, an alert will be set for that zone and all fans within the zone will be set to full speed. The CPU fans have additional cross-failure logic that will set the opposite CPU fan to full speed if one of the CPU fans is disconnected or is non-functional in a dual-CPU system.

If a fan fails during system operation, an alert will be set for that zone and all fans within the zone will be set to full speed. The CPU fans have additional cross-failure logic that will set the opposite CPU fan to full speed if one of the CPU fans fails in a dual-CPU system.

The T2P9D01 factory setpoint for CPU core temperature is 50°C, and the system will attempt to maintain the cores at that temperature even under light or no load. As a result, a lightly loaded system may not benefit from air drawn over the CPU heatsink(s), and mainboard / peripheral cooling predominantly comes from chassis fans in this situation. For this reason, it is important to connect at least one chassis fan providing airflow over the mainboard surface in order to provide cooling for memory modules and other active components.

# Usage

# **INITIAL POWER-ON**

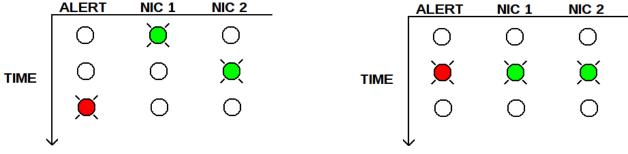

When first applying standby power to the T2P9D01, i.e., when the system is plugged in after being disconnected from power, the internal BMC needs to boot before any other operation request will be accepted. The status of this BMC boot is indicated by two front panel LED patterns:

Illustration 9: BMC Boot Phase 1

Illustration 10: BMC Boot Phase 2

When these patterns have been replaced by normal front panel operation, the system is ready to accept commands.

There are two primary methods of interacting with the OpenPOWER bootloader, serial and graphical. By default, the rear serial port is an active serial console during the IPL process; it may be accessed either via a terminal running at 115,200 baud or via the obmc-console-client application on the BMC. Alternatively, the integrated VGA port and/or any discrete GPUs supported by the internal Linux kernel will allow interaction with the bootloader.

With your choice of peripherals connected for bootloader menu access, press the power button on your chassis. Within a few seconds the system should initiate the IPL cycle, and in about 10 seconds the front panel will start showing IPL status information on the ID / NIC1 / NIC2 LEDs. This front panel status information will override normal front panel indicators until IPL has completed, at which point the system will also emit one short beep to indicate IPL completion.

# **SELECTING A BOOT MEDIUM**

After IPL has completed, you will be presented with the Petitboot main menu. If this system has already been configured with a supported operating system, a boot countdown will start. Pressing any key will abort this countdown and allow interaction with the boot menu. Petitboot currently supports a wide variety of boot media, from TFTP sources to NVMe storage and local SATA / SAS devices; any connected media with a compatible boot structure will be automatically detected and added to the list of boot options.

```

Petitboot (v1.6.6-p9ec043b)

[Network: enP4pls0f0 / 2c:09:4d:00:00:00]

linux

netboot enP4pls0f0 (/pxelinux.0)

System information

System configuration

System status log

Language

Rescan devices

Retrieve config from URL

Plugins (0)

*Exit to shell

Enter=accept, e=edit, n=new, x=exit, l=language, g=log, h=help

```

To select an option, use the arrow keys to move the highlighted entry, then press <Return> to select the highlighted entry. Note that depending on your selected boot medium, you may need to edit the Linux command line parameters before booting via the "e" command. Most current ppc64/ppc64el boot media assumes that the serial console will be the primary method of early and low level I/O; if you are not using the serial console, you may need to adjust the console parameter of the Linux command line appropriately.

#### **BMC ACCESS**

Certain operations require BMC access to execute. The T2P9D01 BMC is attached to network port 1 via NCSI, and is configured to request an IP address via DHCP. Once it is connected and has a valid IP address, you can log in via SSH using the following default credentials:

Username: root Password: 0penBmc

**NOTE:** It is strongly recommended that you change this default password immediately after login via the passwd command on the BMC.

#### **HOST FIRMWARE UPDATES**

Host firmware updates are controlled by the BMC. To update firmware, power down the host system but leave the system connected to wall power. Transfer the PNOR image to the BMC /tmp/directory using scp, then execute pflash -E -p /tmp/<filename>.pnor to update the host firmware.

# **BMC FIRMWARE UPDATES**

BMC firmware updates are controlled by the BMC. To update firmware, power down the host system but leave

the system connected to wall power. Transfer the BMC firmware image to the BMC /tmp/ directory using scp, then execute pflash -b -E -p /tmp/<filename>.pnor to update the BMC firmware.

**NOTE:** When updating early revisions of the BMC firmware, and to a lesser degree during any BMC firmware update, there is a possibility that the update process may result in a non-functional BMC. Recovery of the BMC in this situation would requiring external programming of the socketed BMC Flash ROM, so it may be useful to have an external programming method available before attempting to update the BMC firmware.

# Support

# **GETTING HELP**

If you require assistance operating your T2P9D01, you may contact Raptor Computing Systems technical support directly at <a href="mailto:support@raptorcs.com">support@raptorcs.com</a>. Alternatively, we also have a Wiki and other support resources available online at <a href="https://www.raptorcs.com">https://www.raptorcs.com</a>; the information you require may already be available on one of these resources.